# **MIPS® EJTAG Specification**

Document Number: MD00047 Revision 5.06 March 05, 2011

MIPS Technologies, Inc. 955 East Arques Avenue Sunnyvale, CA 94085-4521

Copyright © 2000-2010 MIPS Technologies Inc. All rights reserved.

Copyright © 2000-2010 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS73, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS-VERIFIED, MIPS-VERIFIED logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24KEf, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004Kc, 1004Kc, 1004Kf, 1074Kc, 1074Kc, 1074Kf, R3000, R5000, R5000, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microMIPS, OCI, PDtrace, the Pipeline, Pro Series, SEAD, SEAD-2, SmartMIPS, SOC-it, System Navigator, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

Template: nB1.03, Built with tags: 2B

# **Table of Contents**

| Cł | apter 1: Overview of the EJTAG System                                  | .13  |

|----|------------------------------------------------------------------------|------|

|    | 1.1: Introduction to EJTAG                                             |      |

|    | 1.2: Historical Perspective                                            |      |

|    | 1.3: EJTAG Capabilities                                                | . 17 |

|    | 1.3.1: Debug Exception and Debug Mode                                  |      |

|    | 1.3.2: Off-board EJTAG Memory                                          |      |

|    | 1.3.3: Debug Breakpoint Instruction                                    |      |

|    | 1.3.4: Hardware Breakpoints                                            |      |

|    | 1.3.5: Single-Step Execution                                           |      |

|    | 1.4: EJTAG Components and Options                                      |      |

|    | 1.4.1: EJTAG Processor Core Extensions                                 |      |

|    | 1.4.2: EJTAG Test Access Port                                          |      |

|    | 1.4.3: Debug Control Register                                          |      |

|    | 1.4.4: Hardware Breakpoint Unit                                        |      |

|    | 1.4.5: Fast Debug Channel                                              |      |

|    | 1.5: Complex Breakpoint and Trigger (CBT) Block                        |      |

|    | 1.6: EJTAG-Specific Coprocessor 0 Registers                            |      |

|    | 1.7: Memory-Mapped EJTAG Registers                                     |      |

|    | 1.7.1: Debug Control Register                                          |      |

|    | 1.7.2: Debug Exception Vector Location                                 |      |

|    | 1.7.3: Load Data Value Register                                        |      |

|    | 1.7.4: Instruction Hardware Breakpoint Registers                       |      |

|    | 1.7.5: Data Hardware Breakpoint Registers                              |      |

|    | 1.7.6: Complex Break and Trigger Registers                             |      |

|    | 1.8: Memory-Mapped EJTAG Memory Segment                                |      |

|    | 1.9: Memory-Mapped Fast Debug Channel Registers                        |      |

|    | 1.10: EJTAG Test Access Port Registers                                 |      |

|    | 1.11: The Implications of Multiprocessing and Multithreading for EJTAG |      |

|    | 1.12: Related Documents                                                |      |

|    | 1.13: Notations and Conventions                                        | . 28 |

|    | 1.13.1: Compliance                                                     | . 28 |

|    | 1.13.2: UNPREDICTABLE and UNDEFINED Operations                         | . 28 |

|    | 1.13.3: Register Field Notations                                       | . 29 |

|    | 1.13.4: Value Notations                                                | . 30 |

|    | 1.13.5: Address Notations                                              | . 30 |

|    |                                                                        |      |

| Cł | napter 2: EJTAG Processor Core Extensions                              |      |

|    | 2.1: Overview                                                          |      |

|    | 2.2: Debug Mode Execution                                              |      |

|    | 2.2.1: Debug Mode Instruction Set                                      |      |

|    | 2.2.2: Debug Mode Address Space                                        |      |

|    | 2.2.3: Debug Mode Handling of Processor Resources                      |      |

|    | 2.2.4: CP0 and dseg Segment Hazards                                    |      |

|    | 2.3: Debug Exceptions                                                  |      |

|    | 2.3.1: Debug Exception Priorities                                      |      |

|    | 2.3.2: Debug Exception Vector Location                                 |      |

|    | 2.3.3: Debug Exception ISA mode                                        | . 43 |

|                          | 2.3.4: General Debug Exception Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                          | 2.3.5: Debug Breakpoint Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45       |

|                          | 2.3.6: Debug Instruction Break Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46       |

|                          | 2.3.7: Debug Data Break Load/Store Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46       |

|                          | 2.3.8: Debug Data Break Load/Store Imprecise Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46       |

|                          | 2.3.9: Debug Single Step Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47       |

|                          | 2.3.10: Debug Interrupt Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49       |

| 2.                       | .4: Debug Mode Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50       |

|                          | 2.4.1: Exceptions Taken in Debug Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51       |

|                          | 2.4.2: Exceptions on Imprecise Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52       |

|                          | 2.4.3: Debug Mode Exception Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52       |

| 2.                       | .5: Interrupts and NMIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53       |

|                          | 2.5.1: Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54       |

|                          | 2.5.2: NMIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54       |

| 2.                       | .6: Reset and Soft Reset of Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54       |

|                          | 2.6.1: EJTAGBOOT Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54       |

|                          | 2.6.2: Reset from Probe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55       |

|                          | 2.6.3: Processor Reset by Probe through Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|                          | 2.6.4: Reset Occurred Indication through Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|                          | 2.6.5: Soft Reset Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|                          | 2.6.6: Reset of Other Debug Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 2                        | .7: EJTAG Coprocessor 0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| _                        | 2.7.1: Debug Register (CP0 Register 23, Select 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|                          | 2.7.2: Debug2 Register (CP0 Register 23, Select 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|                          | 2.7.3: Debug Exception Program Counter Register (CP0 Register 24, Select 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|                          | 2.7.4: Debug Exception Save Register (CP0 Register 31, Select 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 2.                       | .8: EJTAG Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67       |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Chap                     | .8: EJTAG Instructions  oter 3: Debug Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75       |

| Chap<br>Chap             | .8: EJTAG Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75<br>81 |

| Chap<br>Chap             | .8: EJTAG Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

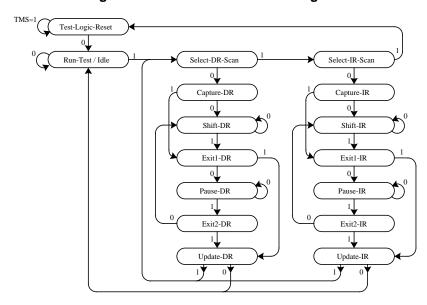

| Char<br>Char<br>4.       | .8: EJTAG Instructions.  oter 3: Debug Control Register  oter 4: EJTAG Test Access Port1: TAP Overview2: TAP Signals 4.2.1: Test Clock Input (TCK) 4.2.2: Test Mode Select Input (TMS) 4.2.3: Test Data Input (TDI) 4.2.4: Test Data Output (TDO) 4.2.5: Test Reset Input (TRST*)3: TAP Controller 4.3.1: Test-Logic-Reset State 4.3.2: Capture-IR State                                                                                                                                                                                                                                                                                            |          |

| Char<br>Char<br>4.       | Debug Control Register  Diter 4: EJTAG Test Access Port  1: TAP Overview  2: TAP Signals  4.2.1: Test Clock Input (TCK)  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI)  4.2.4: Test Data Output (TDO)  4.2.5: Test Reset Input (TRST*)  3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.3: Shift-IR State                                                                                                                                                                                                                                                                                        |          |

| Char<br>Char<br>4.       | Debug Control Register  Diter 4: EJTAG Test Access Port  1: TAP Overview  2: TAP Signals  4.2.1: Test Clock Input (TCK)  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI)  4.2.4: Test Data Output (TDO)  4.2.5: Test Reset Input (TRST*)  3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.4: Update-IR State  4.3.4: Update-IR State                                                                                                                                                                                                                                                               |          |

| Char<br>Char<br>4.       | .8: EJTAG Instructions  oter 3: Debug Control Register  oter 4: EJTAG Test Access Port  .1: TAP Overview  .2: TAP Signals  4.2.1: Test Clock Input (TCK)  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI)  4.2.4: Test Data Output (TDO)  4.2.5: Test Reset Input (TRST*)  .3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.3: Shift-IR State  4.3.4: Update-IR State  4.3.5: Capture-DR State                                                                                                                                                                                                     |          |

| Char<br>Char<br>4.       | Debug Control Register  Deter 4: EJTAG Test Access Port  1: TAP Overview  2: TAP Signals  4.2.1: Test Clock Input (TCK)  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI)  4.2.4: Test Data Output (TDO)  4.2.5: Test Reset Input (TRST*)  3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.4: Update-IR State  4.3.5: Capture-DR State  4.3.6: Shift-DR State  4.3.6: Shift-DR State                                                                                                                                                                                                                |          |

| Char<br>Char<br>4.<br>4. | Debug Control Register  Deter 3: Debug Control Register  Deter 4: EJTAG Test Access Port  1: TAP Overview  2: TAP Signals  4.2.1: Test Clock Input (TCK)  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI)  4.2.4: Test Data Output (TDO)  4.2.5: Test Reset Input (TRST*)  3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.3: Shift-IR State  4.3.4: Update-IR State  4.3.5: Capture-DR State  4.3.6: Shift-DR State  4.3.7: Update-DR State                                                                                                                                                       |          |

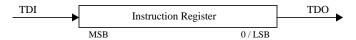

| Char<br>Char<br>4.<br>4. | Deter 3: Debug Control Register  Deter 4: EJTAG Test Access Port  1: TAP Overview  2: TAP Signals  4.2.1: Test Clock Input (TCK).  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI).  4.2.4: Test Data Output (TDO).  4.2.5: Test Reset Input (TRST*).  3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.3: Shift-IR State  4.3.4: Update-IR State  4.3.5: Capture-DR State  4.3.6: Shift-DR State  4.3.7: Update-DR State  4.3.7: Update-DR State  4.3.7: Update-DR State  4.3.7: Update-DR State  4.3.7: Instruction Register and Special Instructions                                             |          |

| Char<br>Char<br>4.<br>4. | Deter 3: Debug Control Register  Deter 4: EJTAG Test Access Port  1: TAP Overview  2: TAP Signals  4.2.1: Test Clock Input (TCK)  4.2.2: Test Mode Select Input (TMS)  4.2.3: Test Data Input (TDI)  4.2.4: Test Data Output (TDO)  4.2.5: Test Reset Input (TRST*)  3: TAP Controller  4.3.1: Test-Logic-Reset State  4.3.2: Capture-IR State  4.3.3: Shift-IR State  4.3.4: Update-IR State  4.3.5: Capture-DR State  4.3.6: Shift-DR State  4.3.7: Update-DR State  4.3.7: Instruction Register and Special Instructions  4.4.1: ALL Instruction |          |

| Chap<br>4.<br>4.         | Deter 3: Debug Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Chap<br>4.<br>4.         | Diter 3: Debug Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Chap<br>4.<br>4.         | Debug Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| Chap<br>4.<br>4.         | Diter 3: Debug Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| 4.5.2: Implementation Register (TAP Instruction IMPCODE)                          | 90      |

|-----------------------------------------------------------------------------------|---------|

| 4.5.3: Data Register (TAP Instruction DATA, ALL, or FASTDATA)                     | 93      |

| 4.5.4: Address Register (TAP Instruction ADDRESS or ALL)                          |         |

| 4.5.5: EJTAG Control Register (ECR) (TAP Instruction CONTROL or ALL)              | 96      |

| 4.5.6: Fastdata Register (TAP Instruction FASTDATA)                               |         |

| 4.5.7: PCsample Register (PCSAMPLE Instruction)                                   | 104     |

| 4.5.8: Bypass Register (TAP Instruction BYPASS, (EJTAG/NORMAL)BOOT, or Unu        | sed)105 |

| 4.6: Examples of Use                                                              |         |

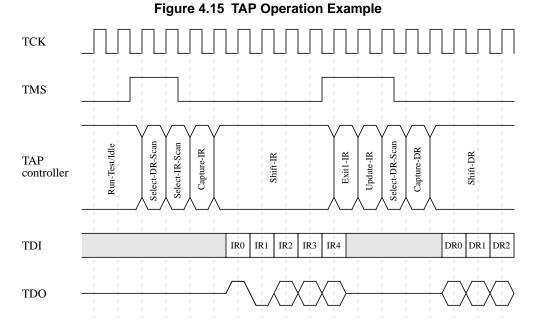

| 4.6.1: TAP Operation                                                              | 105     |

| 4.6.2: ManufID Value                                                              | 106     |

| 4.6.3: Rocc Bit Usage                                                             | 106     |

| 4.6.4: EJTAG Memory Access Through Processor Access                               | 107     |

| Chapter 5: Hardware Breakpoints                                                   | 111     |

| 5.1: Introduction                                                                 |         |

| 5.1.1: Instruction Breakpoint Features                                            |         |

| 5.1.2: Data Breakpoint Features                                                   |         |

| 5.2: Overview of Instruction and Data Breakpoint Registers                        |         |

| 5.2.1: Overview of Instruction Breakpoint Registers                               |         |

| 5.2.2: Overview of Data Breakpoint Registers                                      |         |

| 5.3: Conditions for Matching Breakpoints                                          |         |

| 5.3.1: Conditions for Matching Instruction Breakpoints                            |         |

| 5.3.2: Conditions for Matching Data Breakpoints                                   |         |

| 5.3.3: Precise Exceptions on Data Value Match Breaks                              |         |

| 5.4: Debug Exceptions from Breakpoints                                            |         |

| 5.4.1: Debug Exception Caused by Instruction Breakpoint                           |         |

| 5.4.2: Debug Exception by Data Breakpoint                                         |         |

| 5.5: Breakpoints Used as Triggerpoints                                            |         |

| 5.6: Instruction Breakpoint Registers                                             | 124     |

| 5.6.1: Instruction Breakpoint Status (IBS) Register                               | 125     |

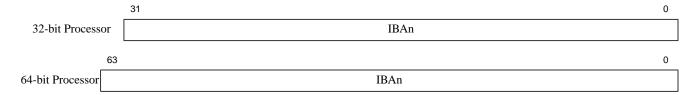

| 5.6.2: Instruction Breakpoint Address n (IBAn) Register                           | 126     |

| 5.6.3: Instruction Breakpoint Address Mask n (IBMn) Register                      | 126     |

| 5.6.4: Instruction Breakpoint ASID n (IBASIDn) Register                           | 127     |

| 5.6.5: Instruction Breakpoint Control n (IBCn) Register                           | 128     |

| 5.7: Data Breakpoint Registers                                                    | 129     |

| 5.7.1: Data Breakpoint Status (DBS) Register                                      | 130     |

| 5.7.2: Data Breakpoint Address n (DBAn) Register                                  |         |

| 5.7.3: Data Breakpoint Address Mask n (DBMn) Register                             | 132     |

| 5.7.4: Data Breakpoint ASID n (DBASIDn) Register                                  |         |

| 5.7.5: Data Breakpoint Control n (DBCn) Register                                  |         |

| 5.7.6: Data Breakpoint Value n (DBVn) Register                                    |         |

| 5.8: Recommendations for Implementing Hardware Breakpoints                        |         |

| 5.8.1: Number of Instruction Breakpoints Without Single Stepping                  |         |

| 5.8.2: Data Breakpoints with Data Value Compares                                  |         |

| 5.8.3: Data Breakpoint Compare on Invalid Data                                    |         |

| 5.8.4: Precise / Imprecise Debug Exceptions on Data Breakpoints with Data Value C | •       |

| 5.9: Breakpoint Examples                                                          |         |

| 5.9.1: Instruction Breakpoint Examples                                            |         |

| 5.9.2: Data Breakpoint                                                            | 138     |

| Chapter 6: Complex Break and Trigger Block                                        | 141     |

| 6.1: Complex Trigger Features/Capabilities                                        |         |

| 6.2: Congral Compley Broak Behavior                                               |         |

| 6.3: Registers in the Complex Break and Trigger Block                                 | 142 |

|---------------------------------------------------------------------------------------|-----|

| 6.3.1: Complex Break and Trigger Control (CBTC) Register (0x8000)                     |     |

| 6.3.2: Instruction Breakpoint Complex Control n (IBCCn) Register (0x1120 + n * 0x100) |     |

| 6.3.3: Instruction Breakpoint Pass Counter n (IBPCn) Register (0x1128 + n*0x100)      |     |

| 6.3.4: Data Breakpoint Complex Control n (DBCCn) Register (0x2128 + n * 0x100)        |     |

| 6.3.5: Data Breakpoint Pass Counter n (DBPCn) Register (0x2130 + n*0x100)             |     |

| 6.3.6: Priming Condition A I/D n (PrCndA/B/C/DI/Dn) Registers                         |     |

| 6.3.7: Stopwatch Timer Control (STCtl) Register (0x8900)                              |     |

| 6.3.8: Stopwatch Timer Count (STCnt) Register (0x8908)                                | 153 |

| 6.4: Tuple Breakpoints                                                                | 153 |

| 6.5: Pass Counters                                                                    | 153 |

| 6.6: Data Qualified Breakpoints                                                       | 154 |

| 6.7: Primed Breakpoints                                                               |     |

| 6.8: Stopwatch Timer                                                                  |     |

| 6.9: Reporting of the Complex Breakpoints in the Debug Register                       |     |

| 6.9.1: Debug Register (23, select 0) Changes for Complex Breakpoints                  |     |

| 6.9.2: Debug2 Register (23, select 6)                                                 | 158 |

| Chapter 7: PC Sampling                                                                | 161 |

| 7.1: Introduction                                                                     | 161 |

| 7.2: PC and Data Address Sampling                                                     | 161 |

| 7.2.1: PC Sampling in Wait State                                                      |     |

| 7.2.2: PC Sampling a MT Processor                                                     |     |

| 7.2.3: Cache Miss PC Sampling                                                         |     |

| 7.2.4: Data Address Sampling                                                          | 163 |

| Chapter 8: Fast Debug Channel                                                         |     |

| 8.1: Overview                                                                         |     |

| 8.2: FDC Features                                                                     |     |

| 8.2.1: Fast Debug Interrupt                                                           |     |

| 8.2.2: FDC TAP Instruction                                                            |     |

| 8.3: Fast Debug Channel Registers                                                     |     |

| 8.3.1: FDC Access Control and Status (FDACSR) Register (Offset 0x0)                   |     |

| 8.3.2: FDC Configuration (FDCFG) Register (Offset 0x8)                                |     |

| 8.3.3: FDC Status (FDSTAT) Register (Offset 0x10)                                     |     |

| 8.3.4: FDC Receive (FDRX) Register (Offset 0x18)                                      |     |

| 8.3.5: FDC Transmit n (FDTXn) Registers (Offset 0x20 + 0x8*n)                         | 172 |

| Chapter 9: On-Chip Interfaces                                                         |     |

| 9.1: Connecting Unused EJTAG Test Access Port and Debug Interrupt Signals             |     |

| 9.2: Optional TRST* Pin                                                               | 173 |

| 9.3: Input Buffers with Pull-Up/Down and Output Drivers for Chip Pins                 |     |

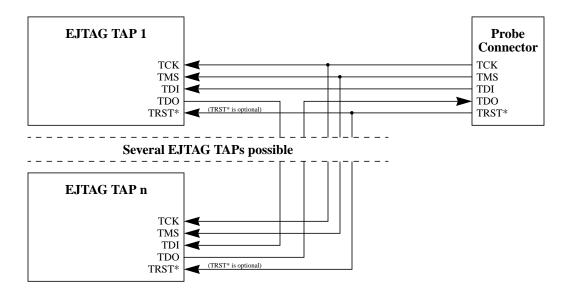

| 9.4: Connecting Multi-Core Test Access Port (TAP) Controllers                         | 174 |

| Chapter 10: Off-Chip and Probe Interfaces                                             |     |

| 10.1: Logical Signals                                                                 |     |

| 10.1.1: Test Access Port Signals                                                      |     |

| 10.1.2: Debug Interrupt Signal                                                        |     |

| 10.1.3: System Reset Signal                                                           |     |

| 10.1.4: Return Test Clock Input                                                       |     |

| 10.1.5: Voltage Sense for I/O Signal                                                  |     |

| 10.2: AC Timing Characteristics                                                       | 178 |

| 10.2.1: Test Access Port Timing                           | 178 |

|-----------------------------------------------------------|-----|

| 10.2.2: Debug Interrupt Timing                            |     |

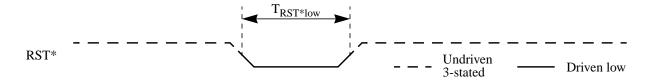

| 10.2.3: System Reset Timing                               |     |

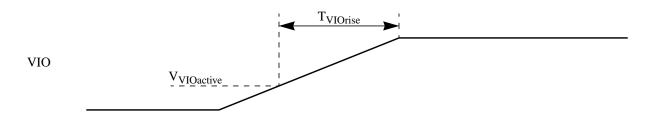

| 10.2.4: Voltage Sense for I/O (VIO) Timing                |     |

| 10.3: DC Electrical Characteristics                       |     |

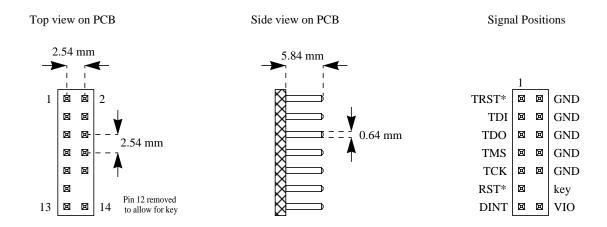

| 10.4: Mechanical Connector                                | 182 |

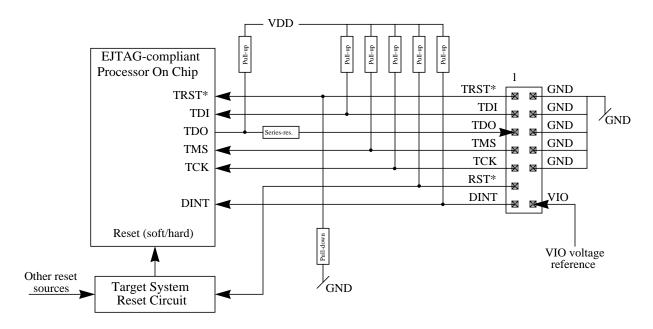

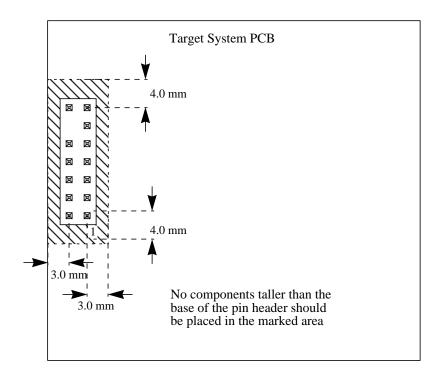

| 10.5: Target System PCB Design                            | 183 |

| 10.5.1: Electrical Connection                             | 183 |

| 10.5.2: Layout Considerations                             | 185 |

| 10.6: Probe Requirements and Recommendations              | 185 |

| 10.6.1: Target System Power-Up with Probe Attached        | 185 |

| 10.6.2: Hot Plug in of Probe                              |     |

| 10.6.3: TDO Level when 3-Stated                           | 186 |

| 10.6.4: RST* Drive by Open Collector                      | 186 |

| 10.6.5: Changing TMS and TDI                              | 186 |

| 10.6.6: Mechanical Connector                              | 186 |

|                                                           |     |

| Appendix A: Differences for R3000 Privileged Environments | 187 |

| A.1: EJTAG Processor Core Extensions                      |     |

| A.1.1: SYNC Instruction                                   |     |

| A.1.2: Debug Exception Vector Location                    |     |

| A.1.3: SYNC Instruction Substitute                        |     |

| A.1.4: CP0 Register Numbers for Debug and DEPC Registers  |     |

| A.2: Hardware Breakpoints                                 |     |

| A.2.1: Instruction Breakpoint Registers                   |     |

| A.2.2: Conditions for Matching Instruction Breakpoints    |     |

| A.2.3: ASID Field in IBCn Register                        |     |

| A.2.4: Data Breakpoint Registers                          |     |

| A.2.5: Conditions for Matching Data Breakpoints           |     |

| A.2.6: ASID Field in DBCn Register                        |     |

| A.3: EJTAG Test Access Port                               | 189 |

| Appendix B: Terminology                                   | 191 |

|                                                           | 100 |

| Appendix C: Functional Clarifications from Old EJTAG 2.5  | 193 |

| Appendix D: Multithreaded and Multi-Core Debug            | 195 |

| D.1: Introduction                                         |     |

| D.2: MCBU Register Map                                    |     |

| D.3: MCBU Registers                                       |     |

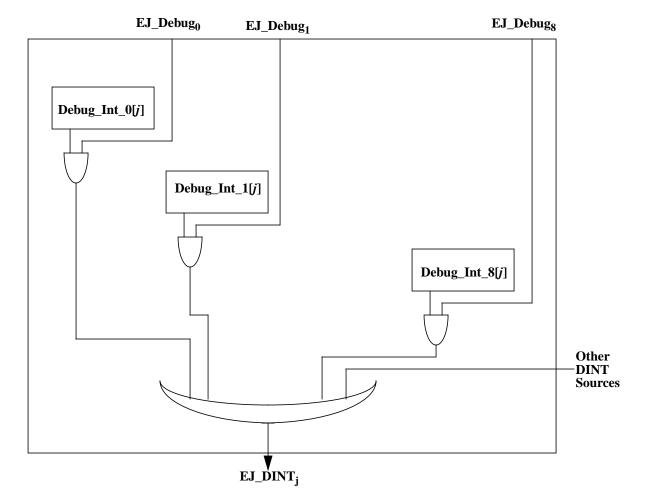

| D.3.1: Debug_Int_i                                        |     |

| D.3.2: Reset                                              |     |

| D.3.3: Debug Interrupt                                    |     |

| D.4: Possible Implementation                              | 190 |

|                                                           | 199 |

| Appendix E: DRSEG Memory Map                              | 200 |

| 11                                                        |     |

| Appendix F: Revision History                              | 203 |

# **List of Figures**

| Figure 1.1: Setup of Debug System without EJTAG                                               | 14  |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 1.2: Setup of Debug System with EJTAG                                                  | 15  |

| Figure 1.3: Test Access Port (TAP) to Internal Connections                                    | 16  |

| Figure 1.4: Simplified Block Diagram of EJTAG Components                                      |     |

| Figure 2.1: Virtual Address Spaces with Debug Mode Segments                                   |     |

| Figure 2.2: DebugVectorAddr Register Format                                                   |     |

| Figure 2.3: Example 1: Single-stepping One Thread TC0 with Non-single-Stepping Thread TC1     |     |

| Figure 2.4: Example 2: Single-stepping Two Threads TC0 and TC1                                |     |

| Figure 2.5: Example 3: Single-stepping Two Threads TC0 and TC1 with Other Threads TC2 and TC3 | 49  |

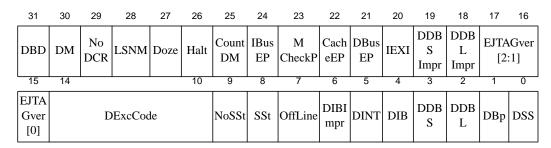

| Figure 2.6: Debug Register Format                                                             |     |

| Figure 2.7: Debug2 Register Format                                                            |     |

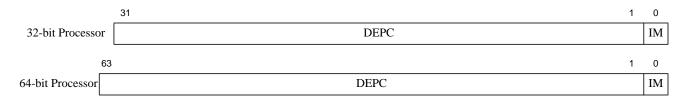

| Figure 2.8: DEPC Register Format                                                              |     |

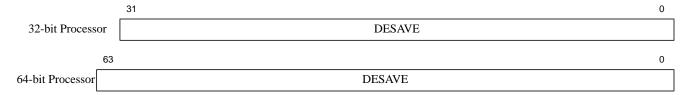

| Figure 2.9: DESAVE Register Format                                                            |     |

| Figure 3.1: DCR Register Format                                                               |     |

| Figure 4.1: Test Access Port (TAP) Overview                                                   |     |

| Figure 4.2: TAP Controller State Diagram                                                      |     |

| Figure 4.3: TDI to TDO Path when in Shift-IR State                                            |     |

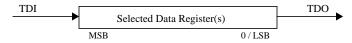

| Figure 4.4: TDI to TDO Path for Selected Data Register(s) when in Shift-DR State              |     |

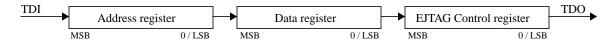

| Figure 4.5: TDI to TDO Path when in Shift-DR State and ALL Instruction is Selected            |     |

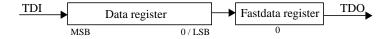

| Figure 4.6: TDI to TDO Path when in Shift-DR State and FASTDATA Instruction is Selected       |     |

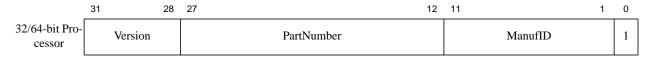

| Figure 4.7: Device ID Register Format                                                         |     |

| Figure 4.8: Implementation Register Format                                                    |     |

| Figure 4.9: Data Register Format                                                              |     |

| Figure 4.10: Address Register Format                                                          |     |

| Figure 4.11: EJTAG Control Register Format                                                    |     |

| Figure 4.12: Fastdata Register Format                                                         |     |

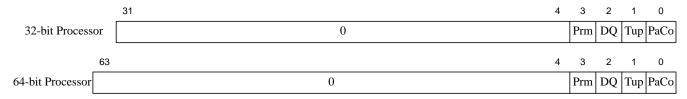

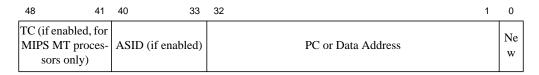

| Figure 4.13: PCsample Register Format                                                         |     |

| Figure 4.14: Bypass Register Format                                                           | 105 |

| Figure 4.15: TAP Operation Example                                                            | 106 |

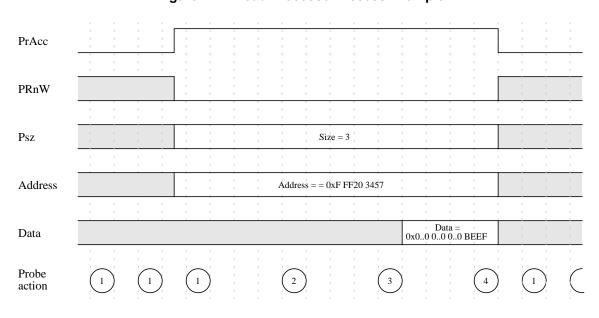

| Figure 4.16: Write Processor Access Example                                                   | 108 |

| Figure 4.17: Read Processor Access Example                                                    | 109 |

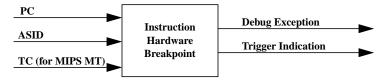

| Figure 5.1: Instruction Breakpoint Overview                                                   |     |

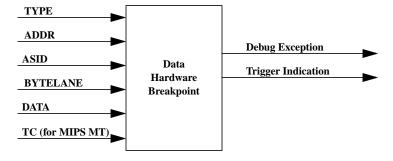

| Figure 5.2: Data Breakpoint Overview                                                          |     |

| Figure 5.3: IBS Register Format                                                               | 125 |

| Figure 5.4: IBAn Register Format                                                              |     |

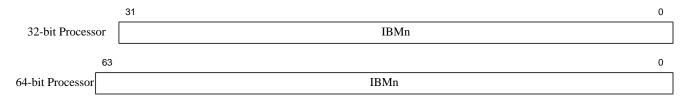

| Figure 5.5: IBMn Register Format                                                              |     |

| Figure 5.6: IBASIDn Register Format                                                           |     |

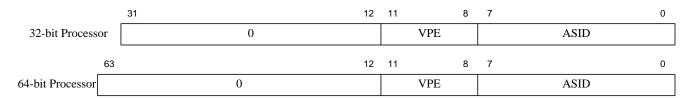

| Figure 5.7: IBCn Register Format                                                              | 128 |

| Figure 5.8: DBS Register Format                                                               |     |

| Figure 5.9: DBAn Register Format                                                              |     |

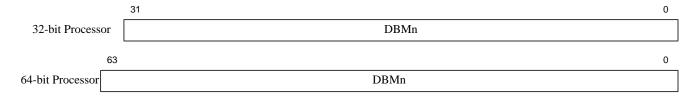

| Figure 5.10: DBMn Register Format                                                             |     |

| Figure 5.11: DBASIDn Register Format                                                          |     |

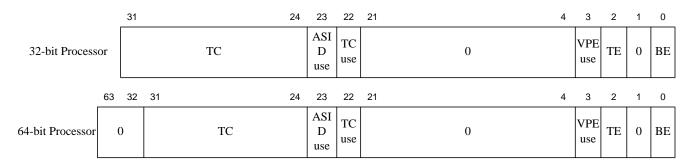

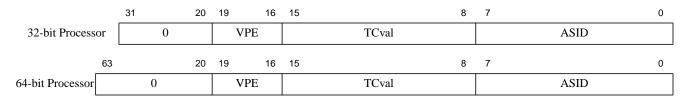

| Figure 5.12: DBCn Register Format                                                             |     |

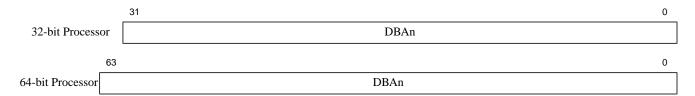

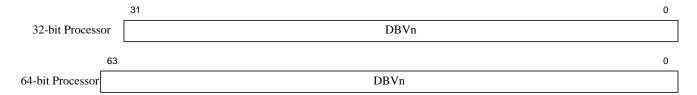

| Figure 5.13: DBVn Register Format                                                             |     |

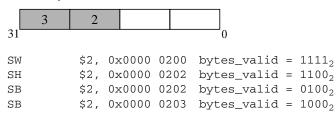

| Figure 5.14: Data Break on Store with Value Compare                                           |     |

| Figure 5.15: Data Break on Store with Value Compare                                           |     |

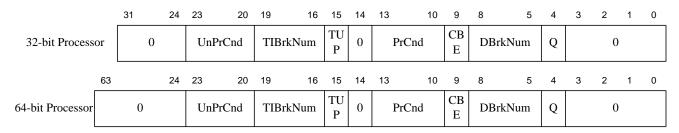

| Figure 6.1: CRTC Register Format                                                              | 143 |

| Figure 6.2: IBCCn Register Format                                   | 145 |

|---------------------------------------------------------------------|-----|

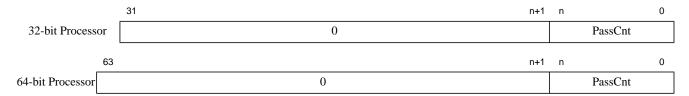

| Figure 6.3: IBPCn Register Format                                   | 146 |

| Figure 6.4: DBCCn Register Format                                   | 147 |

| Figure 6.5: DBPCn Register Format                                   | 149 |

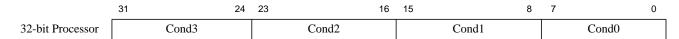

| Figure 6.6: PrCndA Register Format                                  | 150 |

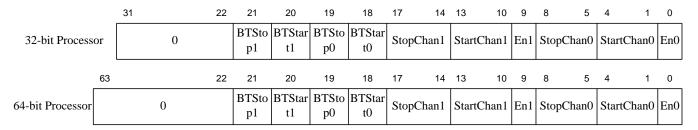

| Figure 6.7: STCtl Register Format                                   | 151 |

| Figure 6.8: STCnt Register Format                                   |     |

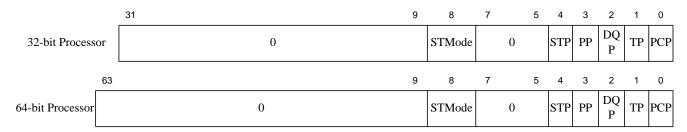

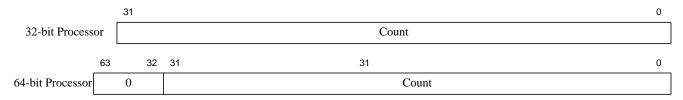

| Figure 7.1: PCSAMPLE TAP Register Format (MIPS32)                   | 162 |

| Figure 7.2: PCSAMPLE TAP Register Format (MIPS64)                   | 162 |

| Figure 8.1: FDC Block Diagram and TDI to TDO Path                   | 168 |

| Figure 8.2: FDC Access Control and Status Register                  | 169 |

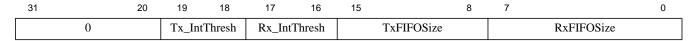

| Figure 8.3: FDC Configuration Register                              | 170 |

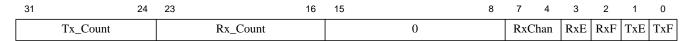

| Figure 8.4: FDC Status Register                                     | 171 |

| Figure 8.5: FDC Receive Register                                    | 172 |

| Figure 8.6: FDC Transmit Register                                   | 172 |

| Figure 9.1: Daisy-chaining of Multi-core EJTAG TAP Controllers      | 174 |

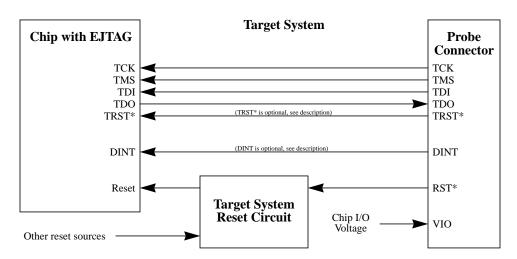

| Figure 10.1: Signal Flow Between Chip, Target System PCB, and Probe | 176 |

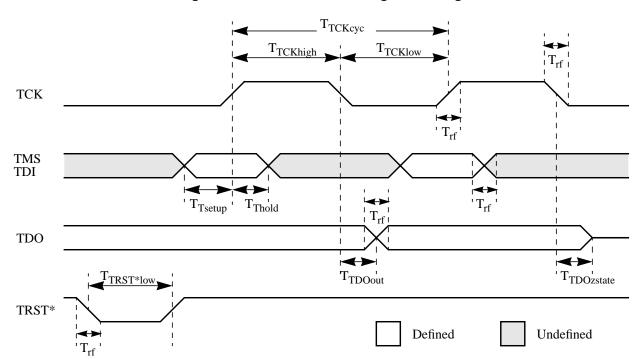

| Figure 10.2: Test Access Port Signals Timing                        | 179 |

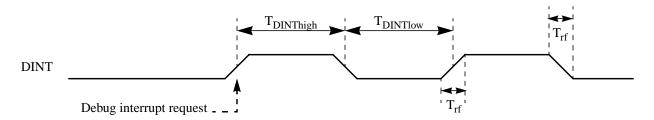

| Figure 10.3: Debug Interrupt Signal Timing                          | 180 |

| Figure 10.4: System Reset Signal Timing                             | 180 |

| Figure 10.5: Voltage Sense for I/O Signal Timing                    | 181 |

| Figure 10.6: EJTAG Connector Mechanical Dimensions                  | 183 |

| Figure 10.7: Target System Electrical EJTAG Connection              | 184 |

| Figure 10.8: Target System Layout for EJTAG Connection              |     |

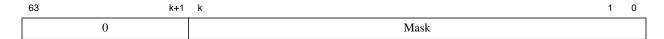

| Figure D.1: Debug_Int_i Register Format                             | 196 |

| Figure D.2: Reset Register Format                                   | 197 |

| Figure D.3: Cold Reset Register Format                              | 197 |

| Figure D.4: NMI Register Format                                     | 198 |

| Figure D.5: Debug Interrupt Register Format                         | 198 |

| Figure D.6: An Example Implementation                               | 199 |

# **List of Tables**

| Table 1.1: EJTAG TAP Instructions                                                 |     |

|-----------------------------------------------------------------------------------|-----|

| Table 1.2: Overview of Coprocessor 0 Registers for EJTAG                          |     |

| Table 1.3: Overview of Debug Control Register as Memory-Mapped Register for EJTAG |     |

| Table 1.4: Overview of Debug Exception Vector Location Register                   |     |

| Table 1.5: Overview of Load Data Value Register                                   |     |

| Table 1.6: Overview of Instruction Hardware Breakpoint Registers                  |     |

| Table 1.7: Overview of Data Hardware Breakpoint Registers                         |     |

| Table 1.8: Overview of Complex Break and Trigger Registers                        | 24  |

| Table 1.9: Overview of Fast Debug Channel Registers                               |     |

| Table 1.10: Overview of Test Access Port Registers                                |     |

| Table 1.11: Register Field Notations                                              |     |

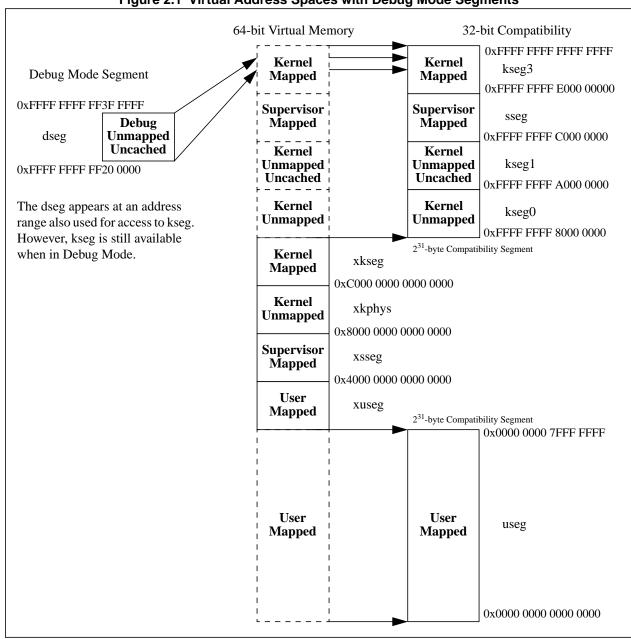

| Table 2.1: Presence of the dseg Segment                                           |     |

| Table 2.2: Physical Address and Cache Attribute for dseg, dmseg and drseg         | 35  |

| Table 2.3: Access to dmseg Segment Address Range                                  | 35  |

| Table 2.4: Access to drseg Segment Address Range                                  | 36  |

| Table 2.5: SYNC and EHB Instruction References                                    |     |

| Table 2.6: Execution Hazards                                                      |     |

| Table 2.7: Hazard Clearing Instructions                                           |     |

| Table 2.8: Priority of Non-Debug and Debug Exceptions                             |     |

| Table 2.9: Debug Exception Vector Location                                        | 42  |

| Table 2.10: DebugVectorAddr Register Field Descriptions                           |     |

| Table 2.11: Exception Handling in Debug Mode                                      |     |

| Table 2.12: Coprocessor 0 Registers for EJTAG                                     |     |

| Table 2.13: Debug Register Field Descriptions                                     | 57  |

| Table 2.14: Debug2 Register Field Descriptions                                    |     |

| Table 2.15: DEPC Register Field Description                                       |     |

| Table 2.16: DESAVE Register Field Descriptions                                    |     |

| Table 3.1: DCR Register Field Descriptions                                        |     |

| Table 4.1: TAP Instruction Overview                                               |     |

| Table 4.2: EJTAG TAP Data Registers                                               |     |

| Table 4.3: Device ID Register Field Descriptions                                  |     |

| Table 4.4: Implementation Register Field Descriptions                             |     |

| Table 4.5: Data Register Field Descriptions                                       |     |

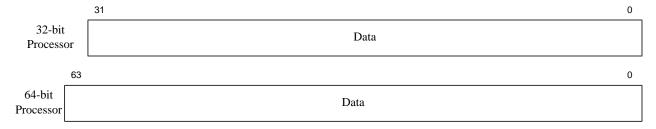

| Table 4.6: Data Register Contents for 32-bit Processors                           |     |

| Table 4.7: Data Register Contents for 64-bit Processors                           |     |

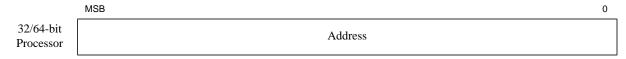

| Table 4.8: Address Register Field Descriptions                                    |     |

| Table 4.9: EJTAG Control Register Field Descriptions                              |     |

| Table 4.10: Combinations of ProbTrap and ProbEn                                   |     |

| Table 4.11: Fastdata Register Field Description                                   |     |

| Table 4.12: Operation of the FASTDATA access                                      |     |

| Table 4.14: Bypass Register Field Description                                     |     |

| Table 4.13: PCsample Register Field Descriptions                                  |     |

| Table 4.15: ManufID Field Value Examples                                          |     |

| Table 4.16: Information Provided to Probe at Processor Access                     |     |

| Table 5.1: Instruction Breakpoint Register Summary                                |     |

| Table 5.2: Data Breakpoint Register Summary                                       |     |

| Table 5.3: Instruction Breakpoint Condition Parameters                            | 115 |

| Table 5.4: Data Breakpoint Condition Parameters                                                   | 116 |

|---------------------------------------------------------------------------------------------------|-----|

| Table 5.5: BYTELANE at Unaligned Address for 32-bit Processors                                    | 119 |

| Table 5.6: BYTELANE at Unaligned Address for 64-bit Processors                                    | 119 |

| Table 5.7: Behavior on Precise Exceptions from Data Breakpoints                                   | 122 |

| Table 5.8: Rules for Update of Break Status (BS) Bits on Precise Exceptions from Data Breakpoints | 122 |

| Table 5.9: Actions Resulting from an Instruction/Data Match for Specified BE and TE Bit Values    |     |

| Table 5.10: Rules for Update of Break Status (BS) Bits on Data Triggerpoints                      |     |

| Table 5.11: Instruction Breakpoint Register Mapping                                               |     |

| Table 5.12: IBS Register Field Descriptions                                                       |     |

| Table 5.13: IBAn Register Field Descriptions                                                      |     |

| Table 5.14: IBMn Register Field Descriptions                                                      |     |

| Table 5.15: IBASIDn Register Field Descriptions                                                   |     |

| Table 5.16: IBCn Register Field Descriptions                                                      |     |

| Table 5.17: Data Breakpoint Register Mapping                                                      |     |

| Table 5.18: DBS Register Field Descriptions                                                       |     |

| Table 5.19: DBAn Register Field Descriptions                                                      |     |

| Table 5.20: DBMn Register Field Descriptions                                                      |     |

| Table 5.21: DBASIDn Register Field Descriptions                                                   |     |

| Table 5.22: DBCn Register Field Descriptions                                                      |     |

| Table 5.23: DBVn Register Field Descriptions                                                      |     |

| Table 6.1: Registers in the Complex Break and Trigger Block and Their drseg Memory Addresses      |     |

| Table 6.2: CBTC Register Field Descriptions                                                       |     |

| Table 6.3: IBCCn Register Field Descriptions                                                      |     |

| Table 6.4: IBPCn Register Field Descriptions                                                      |     |

| Table 6.5: DBCCn Register Field Descriptions                                                      |     |

| Table 6.6: DBPCn Register Field Descriptions                                                      |     |

| Table 6.7: PrCndA Register Field Descriptions                                                     |     |

| Table 6.8: STCtl Register Field Descriptions                                                      |     |

| Table 6.9: STCnt Register Field Descriptions                                                      |     |

| Table 6.10: Addresses for PrCnd[A-D][I/D]N Registers in drseg Memory                              |     |

| Table 6.11: Debug Break Indicator Bits Set for Simple and Complex Breaks                          |     |

| Table 8.1: Cause Register FDC Field Description                                                   |     |

| Table 8.2: IntCtl Register FDC Field Description                                                  |     |

| Table 8.3: Instruction Breakpoint Register Mapping                                                |     |

| Table 8.4: FDC Access Control and Status Register Field Descriptions                              |     |

| Table 8.5: FDC Configuration Register Field Descriptions                                          |     |

|                                                                                                   |     |

| Table 8.6: FDC Status Register Field Descriptions.                                                |     |

|                                                                                                   | 172 |

| Table 8.8: FDC Transmit Register Field Descriptions                                               |     |

| Table 10.1: Test Access Port Signals Overview                                                     |     |

| Table 10.2: Debug Interrupt Signal Overview                                                       |     |

| Table 10.3: System Reset Signal Overview                                                          |     |

| Table 10.4: Voltage Sense for I/O Signal Overview                                                 |     |

| Table 10.5: Voltage Sense for I/O Signal Overview                                                 |     |

| Table 10.6: Test Access Port Signals Timing Values                                                |     |

| Table 10.7: Debug Interrupt Signal Timing Values                                                  |     |

| Table 10.8: System Reset Signal Timing Value                                                      |     |

| Table 10.9: Voltage Sense for I/O Signal Timing Value                                             |     |

| Table 10.10: DC Electrical Characteristics                                                        |     |

| Table 10.11: EJTAG Connector Pinout                                                               |     |

| Table A.1: Debug Exception Vector Location for R3k Privileged Environment Processors              |     |

| Table A.2: Offsets for Instruction Breakpoint Registers for R3k Privileged Environment Processors |     |

| Table A.3: ASID Field in IBCn Register                                                            | 188 |

| Table A.4: Offsets for Data Breakpoint Registers for R3k Privileged Environment Processors | 188 |

|--------------------------------------------------------------------------------------------|-----|

| Table A.5: ASID Field in DBCn Register                                                     | 189 |

| Table D.1: sMCBU Register Memory Map                                                       | 195 |

| Table D.2: MCBU Debug_Int Register Memory Map                                              | 195 |

| Table D.3: Debug_Int_i Register Field Descriptions                                         | 196 |

| Table D.4: Reset Register Field Descriptions                                               | 197 |

| Table D.5: Cold Reset Register Field Descriptions                                          | 197 |

| Table D.6: NMI Register Field Descriptions                                                 | 198 |

| Table D.7: Debug Interrupt Register Field Descriptions                                     | 198 |

| Table F.1: drseg Memory Map.                                                               | 200 |

# Overview of the EJTAG System

This specification describes the behavior and organization of on-chip EJTAG hardware resources as seen by software and by external agents. The software and firmware components of an EJTAG-based debugging environment are outside the scope of this document, as is the underlying physical implementation of EJTAG features.

This chapter contains the following sections:

- Section 1.1, "Introduction to EJTAG"

- Section 1.2, "Historical Perspective"

- Section 1.3, "EJTAG Capabilities"

- Section 1.4, "EJTAG Components and Options"

- Section 1.6, "EJTAG-Specific Coprocessor 0 Registers"

- Section 1.7, "Memory-Mapped EJTAG Registers"

- Section 1.8, "Memory-Mapped EJTAG Memory Segment"

- Section 1.9, "Memory-Mapped Fast Debug Channel Registers"

- Section 1.10, "EJTAG Test Access Port Registers"

- Section 1.11, "The Implications of Multiprocessing and Multithreading for EJTAG"

- Section 1.12, "Related Documents"

- Section 1.13, "Notations and Conventions"

For comments or questions on the EJTAG Architecture or this document, send Email to support@mips.com.

#### 1.1 Introduction to EJTAG

EJTAG is a hardware/software subsystem that provides comprehensive debugging and performance-tuning capabilities to MIPS® microprocessors and to system-on-a-chip components having MIPS processor cores. It exploits the infrastructure provided by the IEEE 1149.1 JTAG Test Access Port (TAP) standard to provide an external interface, and extends the MIPS instruction set and privileged resource architectures to provide a standard software architecture for integrated system debugging.

## 1.2 Historical Perspective

Emulating and debugging embedded hardware and software in a real-world environment remains one of the most difficult tasks facing designers of embedded systems. Embedded microprocessor cores are growing more complex, have increasingly higher performance, and use larger software programs than ever before. To meet the challenge, embedded-systems engineers and programmers must have advanced tools to perform the required levels of in-circuit emulation and debugging.

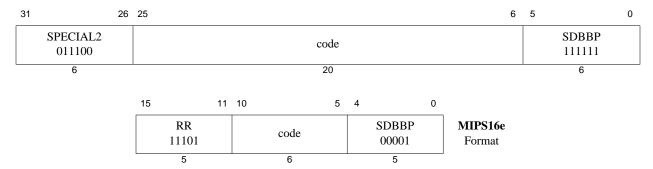

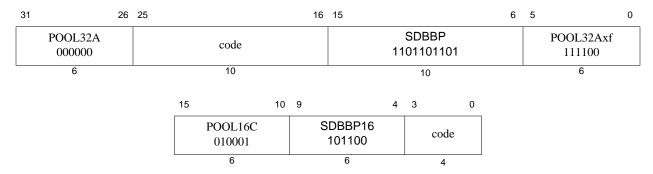

The MIPS architecture has historically provided a set of primitives for debugging software and systems that is consistent with the "RISC" philosophy of integrated hardware/software architecture, providing functionality at a minimum cost in silicon. The base philosophy of integrated MIPS32<sup>®</sup>/MIPS64<sup>®</sup> Instruction Set Architecture (ISA) and MIPS16e<sup>TM</sup> Application Specific Extension (ASE), includes:

- A breakpoint instruction, BREAK, whose execution causes a specific exception.

- A set of trap instructions, whose execution causes a specific exception when certain register value criteria are satisfied.

- A pair of optional Watch registers that can be programmed to cause a specific exception on a load, store, or instruction fetch access to a specific 64-bit doubleword in virtual memory.

- An optional TLB-based MMU that can be programmed to trap on any access, or more specifically, on any store

to a page of memory.

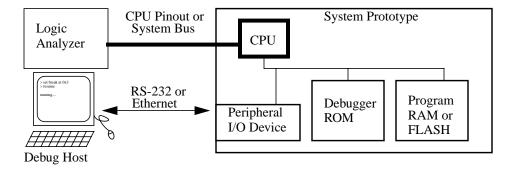

All of these mechanisms assume software support in the form of an operating system, or at least a software monitor, that can modify program memory to insert breakpoints, manipulate the system coprocessor to set watchpoints, and change virtual memory page protection, handle the exceptions produced, and communicate with a user. Additional external hardware tools can supplement these basic mechanisms, such as logic analyzers and in-circuit emulators (ICEs) for additional control and information about program execution. Figure 1.1 shows a possible setup for the debug of an embedded system.

Figure 1.1 Setup of Debug System without EJTAG

While this model of debug works well for many sorts of system, it has the following shortcomings when the system to be debugged is a highly-integrated design:

• System-On-a-Chip (SOC) component design no longer provides an external interface to the processor pin-out or system bus, making the use of logic analyzers and ICEs difficult to impossible.

- Debugging based on software breakpoints or the insertion of trap-on-condition instructions assumes that programs reside in RAM. It is impractical for fully ROM-based systems and assumes support in the O/S for these techniques.

- For consumer electronic applications, a communication port like Ethernet or RS-232 serves no purpose beyond software debug and adds disproportionately to the cost and size of the design.

- Similarly, the ROM necessary to support a debug software monitor on a consumer electronic application could add unacceptable costs.

One alternative to ICE is a specially-packaged device that is a bond-out of the chip. But this solution has the disadvantage of adding to overall product development cost. It also adds the extra requirement of a specially-designed PCB that is needed to access the signals available only on the development chip.

On-Chip Debug (OCD) provides a solution for all these issues, and the EJTAG Debug Solution defines an advanced and scalable feature-set for OCD that allows debugging while executing CPU code at full speed.

One could say that OCD puts the ICE functionality on the chip. Although OCD does add a little extra die area for features that are only required during development, the die area is minimal. More importantly, with development time and overall time-to-market becoming increasingly critical, the trade-off between die area and time seems reasonable.

Having the debug solution on-chip also makes it possible to use it for software upgrades, field testing, and for diagnostics in the final product.

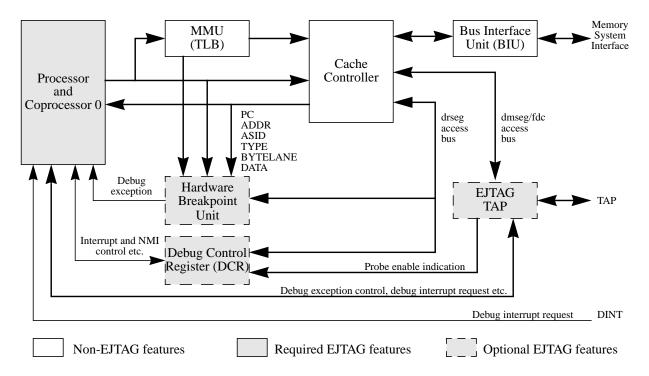

EJTAG supplements the MIPS Architecture in dealing with these problems. A processor or system-on-a-chip implementing EJTAG can be tied into a JTAG scan chain and comprehensively debugged using an external EJTAG probe connected to the system's JTAG TAP interface, as shown in Figure 1.2.

System Prototype Ethernet Other CPU RS-232 EJTAG probe JTAG TAP System with etc. interface Logic

JTAG scan chain

**EJTAG** SOC ASIC/ASSP

Figure 1.2 Setup of Debug System with EJTAG

TAP access

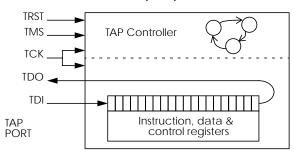

EJTAG uses the five-pin interface defined in IEEE 1149.1 JTAG, which forms the Test Access Port (TAP). The five pins (TRST, TCK, TMS, TDI, and TDO) can be reused to limit pin count if the TAP is on-chip for some other purpose.

Debug host

Figure 1.3 Test Access Port (TAP) to Internal Connections