WARSAW UNIVERSITY OF TECHNOLOGY Electronics and Information Technologies Faculty Research Group on Biocybernetic Aparatus Institute of Electronic Systems

> Tomasz Bolesław CEDRO Index number: 188597

## Master of Science Diploma Thesis

# CeDeROM Brain Computer Interface

Thesis Supervisor: prof. dr hab. Antoni GRZANKA

> November 10, 2011 Warsaw, Poland

#### CeDeROM Brain Computer Interface Abstract

Brain Computer Interface is a biomedical equipment used to perform user interaction with computer equipment based on a brain activity mesurement. Modular Research System presented in this document is a prototype aimed for supporting the research groups with versatile and flexible hardware platform for BCI research, but also easy construct and verification of commercial products that can find its use in solving various real life problems.

Modular design consists of control boards based on STM32 ARM-Cortex M3 for mobile applications and FPGA for real time DSP, safe power supply with galvanic separation, general purpose hex 24-bit SigmaDelta ADC, integrated biological signal acquisition frontend with 24-bit SigmaDelta ADC and SPI interface, standard EEG electrodes connector board, user interaction with LED and push-buttons, and finally the demonstration expansion board with computer joystic interface to control external hardware.

System is equipped with USB2.0 FullSpeed Device Unit (ARM) and 1GBit Ethernet Controller (FPGA). System was designed to be a low-cost solution based on Free and/or Open-Source Software. Example usecases are also presented in this document.

Keywords: CeDeROM BCI (Brain Computer Interface), Neural Interface, Biocybernetics, Biomedical, Neurofeedback, Biofeedback, ARM, Cortex, FPGA, ADC, DSP, OpenEEG, Open-Source, FreeBSD, USB, Matlab Driver, BCIOP, Atari, PONG.

#### Interfejs Mózg–Komputer "CeDeROM BCI" Streszczenie

Interfejs Mózg–Komputer (Brain Computer Interface) jest urządzeniem biomedycznym nakierowanym na interakcję użytkownika ze sprzętem komputerowym za pomocą pomiaru aktywności elektrycznej mózgu. Modularny System Badawczy zaprezentowany w niniejszym dokumencie to prototyp, którego zadaniem jest wsparcie grup badawczych wszechstronną i elastyczną platformą sprzętową do badań nad BCI, ale również łatwe opracowanie i weryfikacja komercyjnych urządzeń, które mogą być pomocne w rozwiązywaniu problemów z życia codziennego.

Na modułową konstrukcję składa się jednostka sterująca oparta o mikrokontroler STM32 z rdzeniem ARM-Cortex M3 dla zastosowań mobilnych oraz układ Xilinx Spartan FPGA dla przetwarzania sygnałów w czasie rzeczywistym, bezpieczny moduł zasilania z separacją galwaniczną, ośmiokanałowy przetwornik analogowo-cyfrowy 24bit SigmaDelta, zintegrowany układ pomiaru i akwizycji sygnałów biologicznych z przetwarzaniem SigmaDelta 24-bit oraz interfejsem SPI, standardowy moduł połączeniowy dla elektrod EEG, układ interakcji z użytkownikem w postaci zestawu przycisków i diod świecących, a także demonstracyjna płytka z modułem interfejsu joysticka sterującego zewnętrznym sprzętem komputerowym.

System wyposażony jest w interfejsy komunikacyjne USB2.0 (moduł ARM) oraz 1GBit kontroler Ethernet (moduł FPGA). System został zaprojektowany jako niedrogie rozwiązanie korzystające z wolnego oprogramowania (Free–Software) o swobodnym dostępie do kodu źródłowego (Open–Source). Przykładowe zastosowania przedstawiono w końcowej części dokumentu.

Słowa kluczowe: BCI, Interfejs Mózg Komputer, Interfejs Neuronalny, Biocybernetyka, Inżynieria Biomedyczna, Neurofeedback, Biofeedback, ARM, Cortex, FPGA, ADC, DSP, OpenEEG, Open-Source, FreeBSD, USB, Ethernet, Matlb/Octave/SciLab, BCIOP, Atari, PONG. To My Family, To My Friends Thank You! I Love You! :-) OM MANI PEME HUNG

## Foreword

Human organism and its information processing abilities are limited. It is also still very susceptible to cellular malfunction, organic diseases and mechanical injuries. There are situations were even whole parts of the body become inactive when others are still functional. In this case interconnecting biological organism with biomedical equipment is the only way to maintain missing functionality or the human life itself.

What is the purpose of life with no communication ability, especially with other people, family, friends, when we cannot share our knowledge, experiences and ideas. Sometimes the information exchange is impossible because of some dysfunction, sometimes the human body limitations itself are the boundaries of our cognition.

The science–fiction unfortunately is still far from reality – today we cannot visit a harsh environment within a cybernetic avatar, or become a spaceship probe controlled directly with our perception from Earth. This however could be possible with advancement of Brain Computer Interfacing technology serving as a gateway between world of biology and technology.

There are two general types of modern BCI – invasive and noninvasive – depending on the techniqie applied for signal acquisition from the tissue. Noninvasive devices acquire biological signals from outside of the human body. This can be done with use of various tomography methods (such as fMRI), or simply electrodes being sticked with conducting paste on top of the skin reading electrical activity of the inside organ situated below – just like ElectroCardioGraphy (ECG) reads heart's work cycle, or ElectroEncephaloGraphy (EEG) reads electrical activity of a brain. Invasive methods requires electrodes (or more general sensors) to be implanted directly into the organ/tissue, therefore it is impossible in amateur applications, especially in an early stage of academic research. Both approaches requires great amount of interdisciplinary knowledge, well coordinated team of highly skilled enthusiasts, legal support, proper funding and laboratory equipment.

Because high-end equipment is not available for amateur/academic research due to extremely high prices, while free and open solution does not provide minimal functional level, this document presents results of a research aimed at creating inexpensive but versatile modular hardware BCI platform. This work is a proof of concept that such system can become a reality with use of commercial off the shelf components and the Open–Source software tools, some basic laboratory equipment, determination and knowledge.

Research results clearly show that there is still even more to accomplish than already has been done. Some parts of this research are pioneering solutions that allow some other solutions to exist in the first place, but has not yet been done before, especially in open manner. Modular design allows easy system reconfiguration for both scientific research and the commercial implementation. Experience gained during all those experiments allowed to identify and overcome some problems at this stage, but also forced me to leave some tasks for closer inspection in near future. All small failures and successful achievements finds my acceptance and submission because they help me to better realize facts, understand surrounding world, and hopefully produce better results.

# Contents

| 1 | Kno  | ow-How                                                                                                              | 11 |

|---|------|---------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Reasons, Problems, Solutions                                                                                        | 11 |

|   | 1.2  | Biological Signal Amplifiers                                                                                        | 12 |

|   | 1.3  | System Configuration and Methodology                                                                                | 13 |

|   | 1.4  | EEG 10-20 system                                                                                                    | 15 |

|   | 1.5  | OpenEEG and other BCI Platforms                                                                                     | 16 |

|   | 1.6  | FreeBSD – Operating System of a choice                                                                              | 18 |

|   | 1.7  | GNU ARM Toolchain                                                                                                   | 19 |

|   | 1.8  | Free Real Time Operating System                                                                                     | 20 |

|   |      | 1.8.1 Introduction                                                                                                  | 20 |

|   |      | 1.8.2 API Fundamentals                                                                                              | 20 |

|   | 1.9  | Universal Serial Bus                                                                                                | 22 |

|   |      | 1.9.1 Introduction                                                                                                  | 22 |

|   |      | 1.9.2 Standards                                                                                                     | 23 |

|   |      | 1.9.3 Physical Signalling                                                                                           | 24 |

|   |      | 1.9.4 Power Management                                                                                              | 24 |

|   |      | 1.9.5 USB Procotol                                                                                                  | 25 |

|   |      | 1.9.6 USB Transfer Modes                                                                                            | 26 |

|   |      | 1.9.7 Bandwidth Mangement                                                                                           | 27 |

|   |      | 1.9.8 USB Descriptors                                                                                               | 27 |

|   | 1.10 | Device Drivers in Matlab                                                                                            | 28 |

|   |      | 1.10.1 Introduction $\ldots$       | 28 |

|   |      | 1.10.2 How Matlab handles execution                                                                                 | 28 |

|   |      | 1.10.3 Dynamic Libraries Matlab Intefrace                                                                           | 29 |

|   |      | 1.10.4 Using Dynamic Libraries                                                                                      | 29 |

|   |      | 1.10.5 Example                                                                                                      | 30 |

|   | 1.11 | Serial Wire Debug                                                                                                   | 31 |

|   |      | 1.11.1 Serial Wire Debug Technical Reference                                                                        | 32 |

|   |      | 1.11.2 LibSWD – Serial Wire Debug Open Library                                                                      | 47 |

|   |      | 1.11.3 LibSWD in practice $\ldots$ | 50 |

|   |      | 1.11.4 LibSWD integration with UrJTAG                                                                               | 50 |

|   |      | 1.11.5 LibSWD integration with OpenOCD                                                                              | 55 |

|   | 1.12 | JTAG / IEEE1149.1                                                                                                   | 58 |

CeDeROM Brain Computer Interface

|          |       | 1.12.1         | JTAG Technical Reference                             | 58       |

|----------|-------|----------------|------------------------------------------------------|----------|

|          |       |                | JTAG Data Register (DR)                              | 62       |

|          | 1.13  |                | Computer Interface Open Protocol                     | 64       |

|          | 1.10  |                | Introduction                                         | 64       |

|          |       |                | BCIOP Overwiew                                       | 65       |

|          |       |                | BCIOP Packet Details                                 | 66       |

|          | 1 14  |                | Software and Hardware                                | 71       |

|          | 1.11  |                | Introduction to FPGA programming                     | 72       |

|          |       |                | Known issues                                         | 72       |

|          |       |                | Installing Linux version of Xilinx ISE on FreeBSD OS | 72 72    |

|          |       |                | Programming the FPGA target device                   | 75       |

|          | 1 1 5 |                | atics and PCB design with Eagle CAD                  | 73<br>77 |

|          | 1.10  |                | Creating new components and libraries                | 78       |

|          |       |                | Exporting design for manufacturing                   | 79       |

|          |       |                | Running Linux Eagle CAD on FreeBSD                   | 79<br>79 |

|          | 1 16  |                |                                                      | 79<br>80 |

|          | 1.10  |                | Crafting                                             | 80<br>81 |

|          |       |                | Photo-litography                                     | 81<br>81 |

|          |       |                | Copper Etching                                       |          |

|          |       |                | Drills Metalization                                  | 83       |

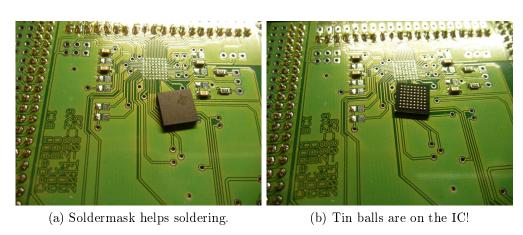

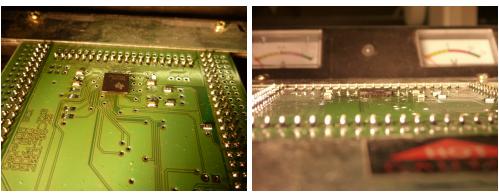

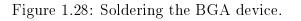

|          |       | 1.10.4         | BGA Soldering                                        | 83       |

| <b>2</b> | Solu  | tion A         | Approach                                             | 86       |

|          | 2.1   |                | on Approach                                          | 86       |

|          |       | 2.1.1          | Introduction                                         | 86       |

|          |       | 2.1.2          | Similar solutions                                    | 87       |

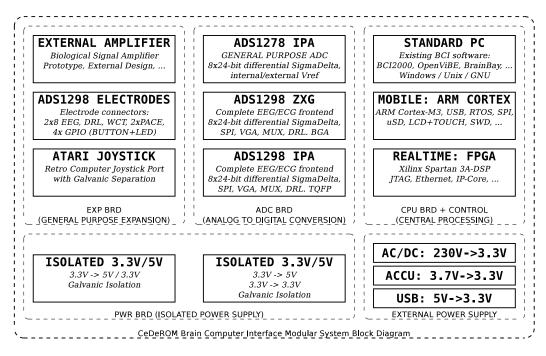

|          |       | 2.1.3          | Block Diagram                                        | 88       |

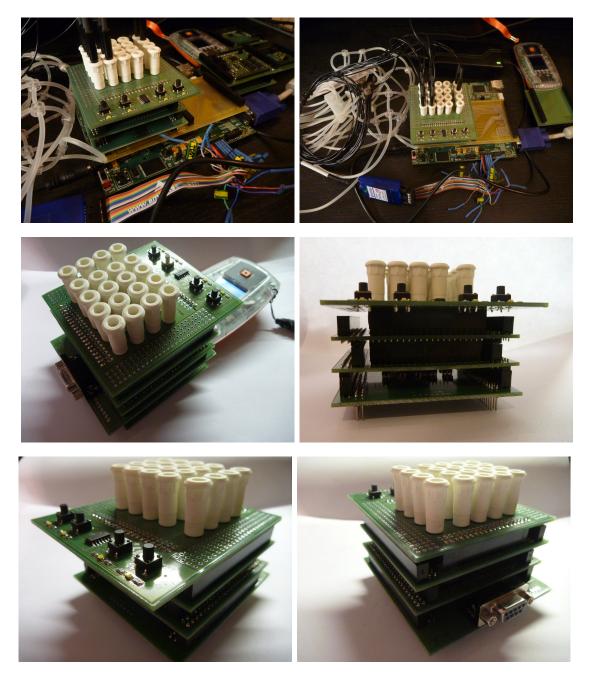

|          |       | 2.1.4          | Hardware Implementation                              | 89       |

|          |       | 2.1.5          | Software Implementation                              | 89       |

|          | 2.2   |                | es Description                                       | 89       |

|          |       | 2.2.1          | CPU_BRD: Xilinx Spartan–3A DSP FPGA                  | 89       |

|          |       |                | CPU BRD: Stm32Primer2 (ARM Cortex-M3)                |          |

|          |       | 2.2.3          | ADP_BRD: QSE to Goldpin Adapter                      | 92       |

|          |       | 2.2.4          | ADP_BRD: Stm32Primer2                                | 92       |

|          |       | 2.2.5          | $PWR_BRD$ : Isolated $3.3V/5V$                       | 97       |

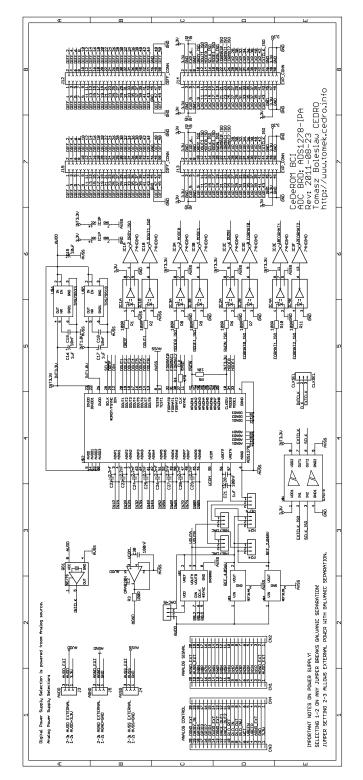

|          |       | 2.2.6          | ADC_BRD: ADS1298                                     | 97       |

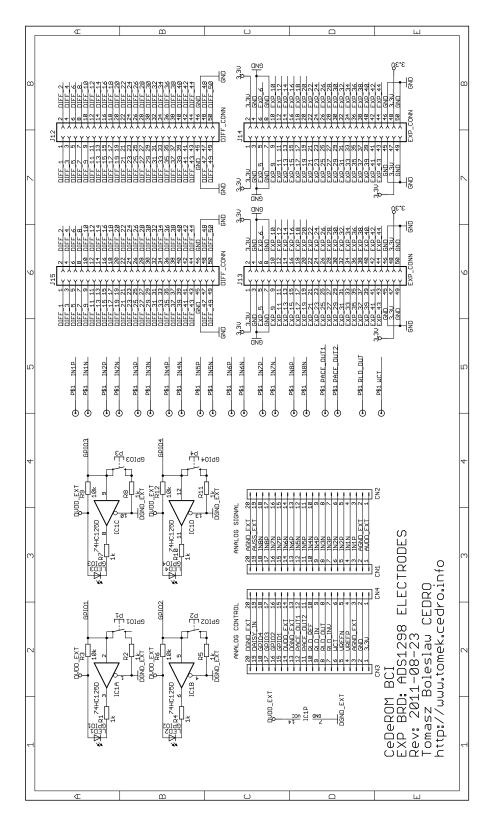

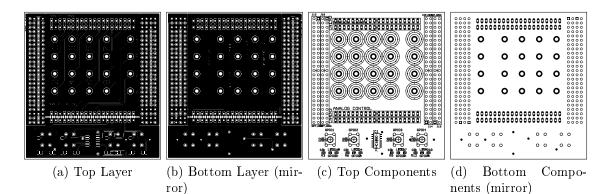

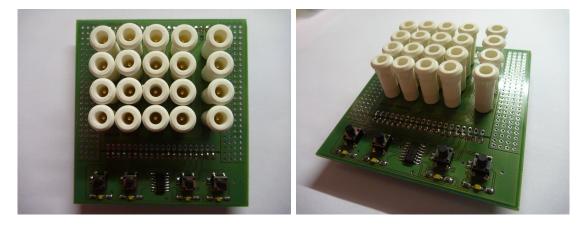

|          |       | 2.2.7          | EXP BRD: ADS1298 Electrodes                          |          |

|          |       | 2.2.8          | ADC_BRD: ADS1278                                     |          |

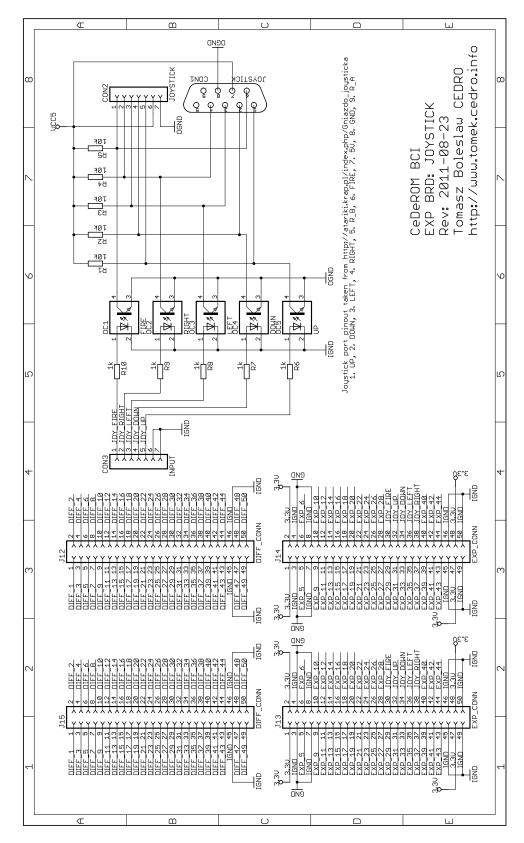

|          |       | 2.2.0<br>2.2.9 | EXP BRD: Atari Joystick                              |          |

|          | 2.3   |                | ble Usecases                                         |          |

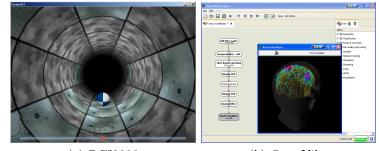

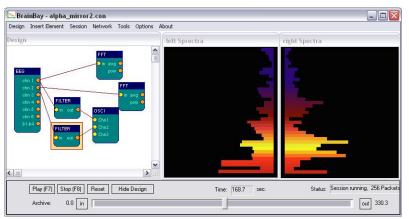

|          | 2.0   | 2.3.1          | Standalone FPGA Application                          |          |

|          |       | 2.3.1<br>2.3.2 | Standalone BCI–PONG Videogame                        |          |

|          |       | 2.3.2<br>2.3.3 | Universal Joystick Controller                        |          |

|          |       | 2.3.3<br>2.3.4 | Modern OpenEEG Replacement                           |          |

|          |       | $_{2.0.4}$     |                                                      | 114      |

| 3 | Summary | and Conclusions      | 117 |

|---|---------|----------------------|-----|

|   | 2.3.6   | Integrated Solutions | 116 |

|   | 2.3.5   | Mobile Holter        | 116 |

# List of Figures

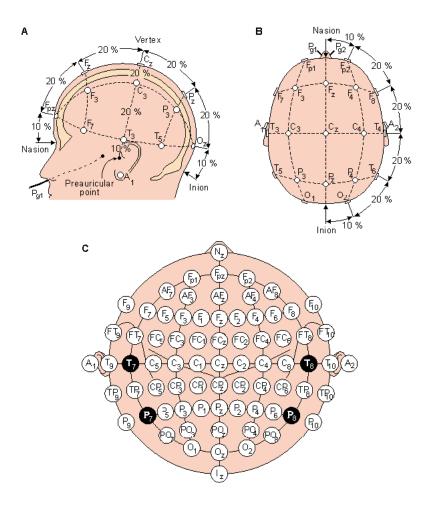

| 1.1  | 10–20 EEG Electrode Placement Diagram [85]                               | 15 |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Commercial low-cost BCI devices for home use.                            | 16 |

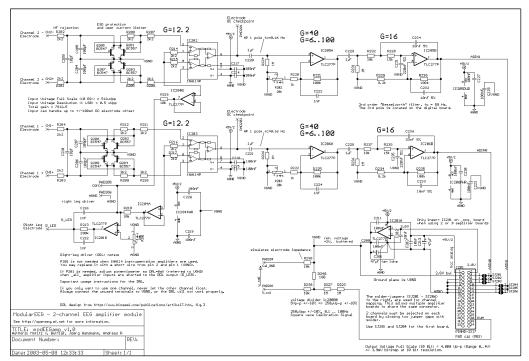

| 1.3  | OpenEEG Schematics.                                                      | 17 |

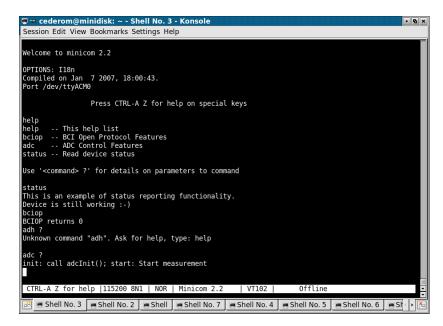

| 1.4  | Command Line Interface (CLI) implemented on LPC2148 ARM–based mi-        |    |

|      | crocontroller with built-in USB Device Controller using OpenSource pro-  |    |

|      | grams                                                                    | 23 |

| 1.5  | Host centric USB bus organisation                                        | 25 |

| 1.6  | USB Device Descriptors organisation diagram                              | 27 |

| 1.7  | Successful write operation [46].                                         | 34 |

| 1.8  | Successful read operation [46]                                           | 36 |

| 1.9  | WAIT response to Read or Write operation request [46]                    | 37 |

| 1.10 | FAULT response to Read or Write operation request [46]                   | 38 |

| 1.11 | Protocol error sequence [46]                                             | 38 |

|      | Protocol error sequence [46] when Sticky Overrun Detection is enabled    | 39 |

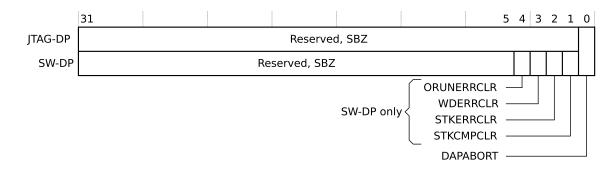

|      | <b>ABORT</b> register map [46]                                           | 40 |

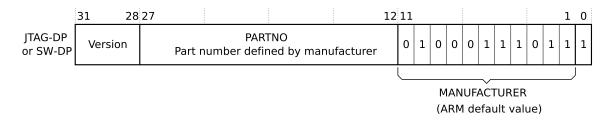

| 1.14 | <b>IDCODE</b> register map [46]                                          | 41 |

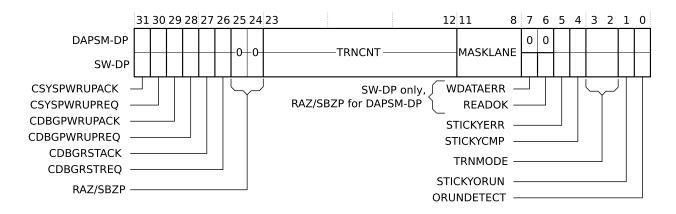

| 1.15 | CTRL/STAT register map [46]                                              | 42 |

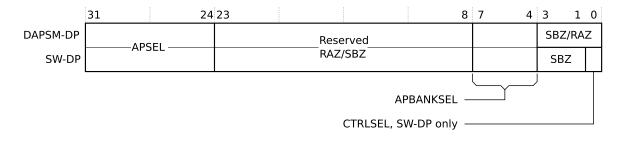

| 1.16 | SELECT register map $[46]$                                               | 44 |

|      | WCR register map [46]                                                    | 46 |

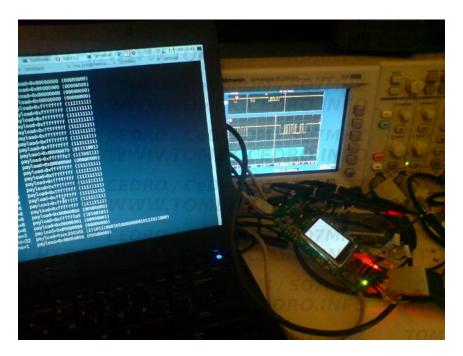

|      | Tapping jtag/swd interface into physical signals                         | 51 |

|      | LibSWD communicating with Stm32Primer2 using UrJTAG drivers              | 52 |

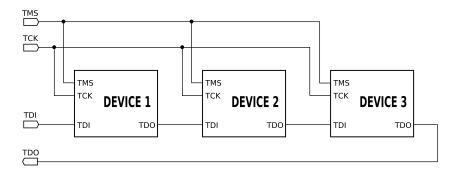

|      | Daisy-chaining JTAG multiple devices [22]                                | 60 |

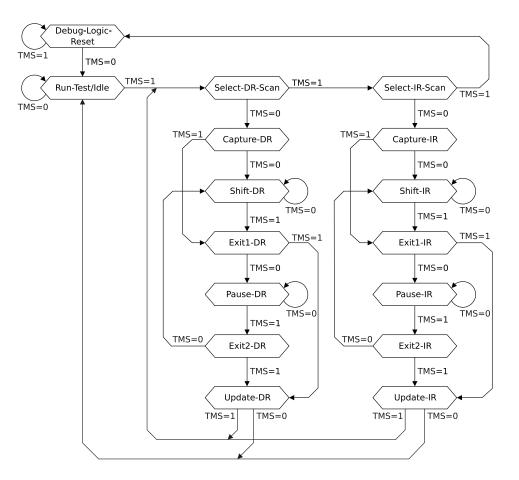

|      | JTAG State Machine [46]                                                  | 61 |

| 1.22 | Xilinx ISE Design Suite installation spash screen. Linux binary working  |    |

|      | on FreeBSD operating system                                              | 74 |

|      | Xilinx ISE Design Suite components readu for use on FreeBSD              | 74 |

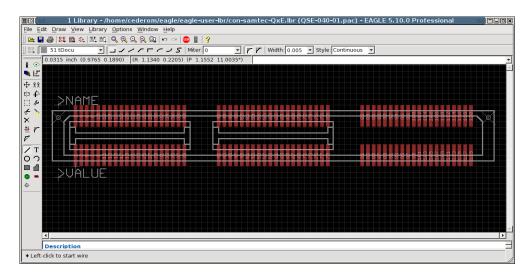

|      | Creating new components for Eagle CAD with integrated components editor. | 79 |

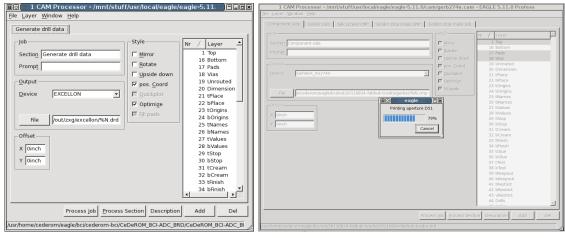

|      | Generating Eagle CAD project documentation for manufacturing             | 80 |

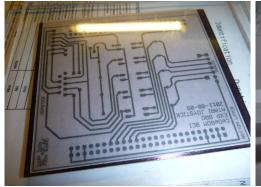

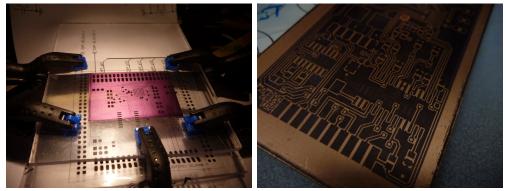

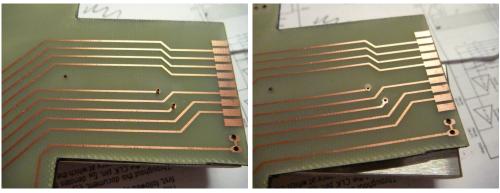

|      | Home made photo-litography                                               | 82 |

|      | Home made mechanical metalization.                                       | 83 |

| 1.28 | Soldering the BGA device                                                 | 84 |

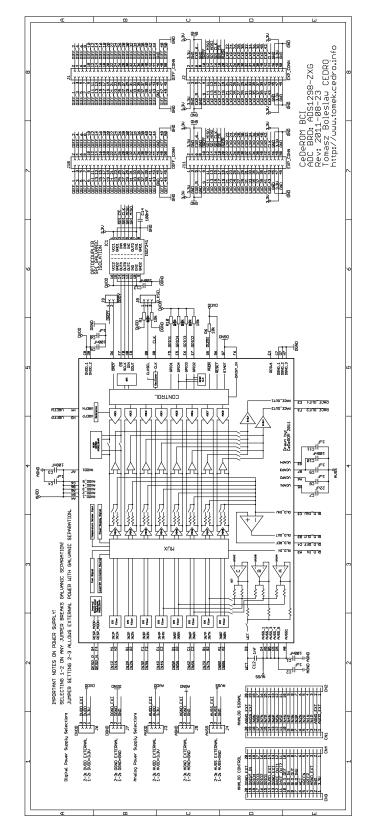

| 2.1  | CeDeROM BCI Block Diagram.                                               | 87 |

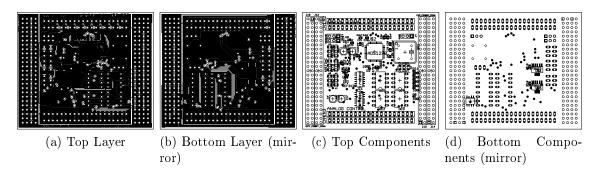

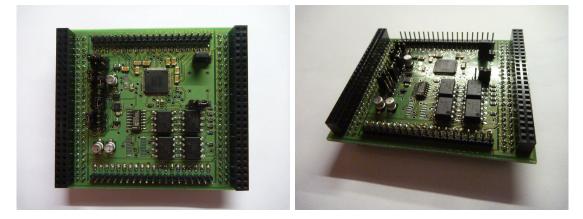

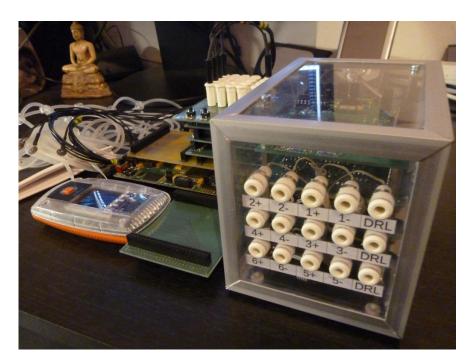

| 2.2  | CeDeROM BCI Assembled Circuit Boards                                     | 90 |

|      |                                                                          |    |

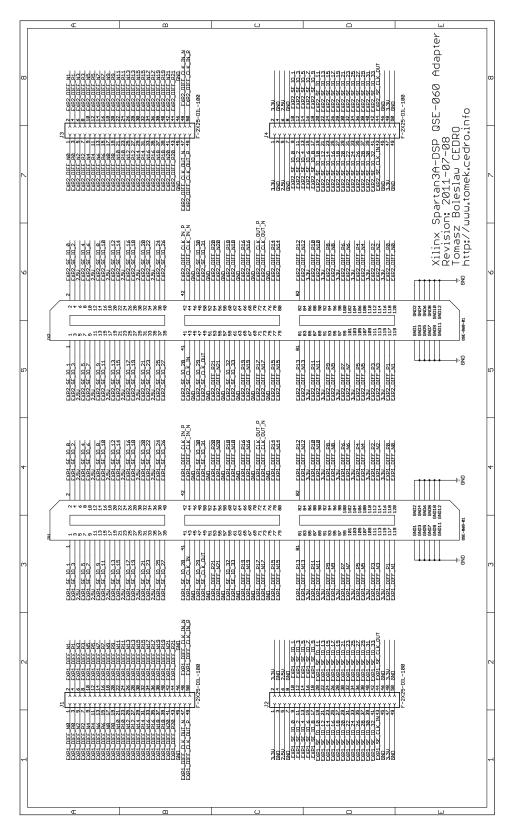

| 2.3  | Xilinx Spartan 3A–DSP Development Board                                                                                                            | 1 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2.4  | Xilinx Spartan 3A–DSP Development Board QSE–to–Goldpin adapter schemat-                                                                            |   |

|      | ics                                                                                                                                                |   |

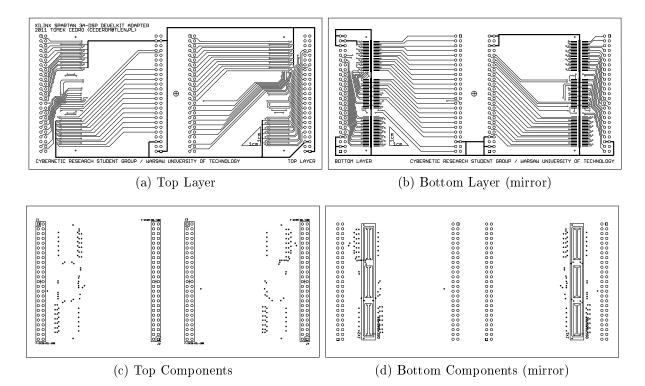

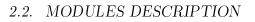

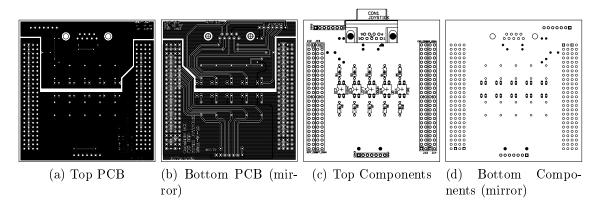

| 2.5  | CeDeROM BCI Xilinx Spartan 3A–DSP Development Board QSE–to–                                                                                        |   |

|      | Goldpin adapter PCB design                                                                                                                         | 4 |

| 2.6  | Assembled QSE-to-Goldpin CeDeROM BCI ADP_BRD for Xilinx Spar-                                                                                      |   |

|      | tan 3A–DSP Development Board                                                                                                                       | 4 |

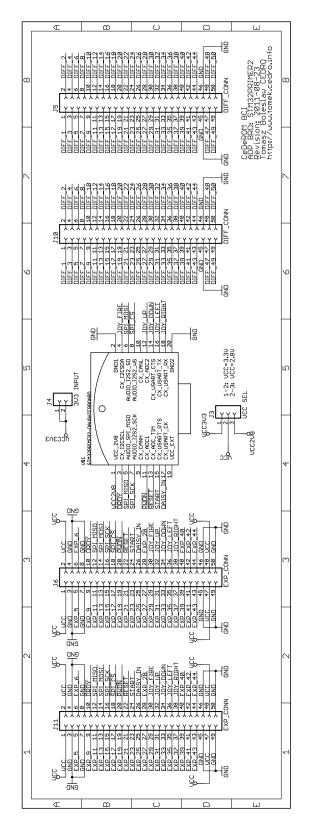

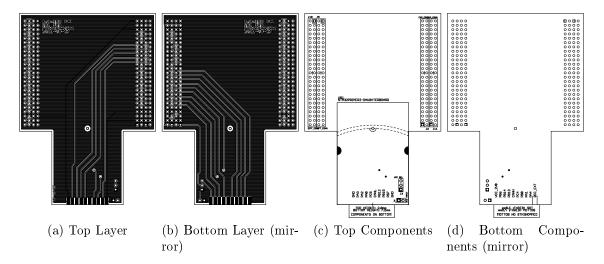

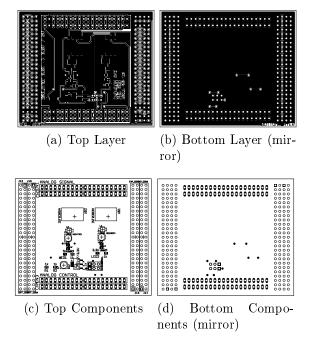

| 2.7  | CeDeROM BCI Stm32Primer2 Adapter Board                                                                                                             | 5 |

| 2.8  | CeDeROM BCI Stm32Primer2 Adapter Board PCB design 9                                                                                                | 6 |

| 2.9  | CeDeROM BCI Stm32Primer2 Adapter Board, assembled 9                                                                                                | 6 |

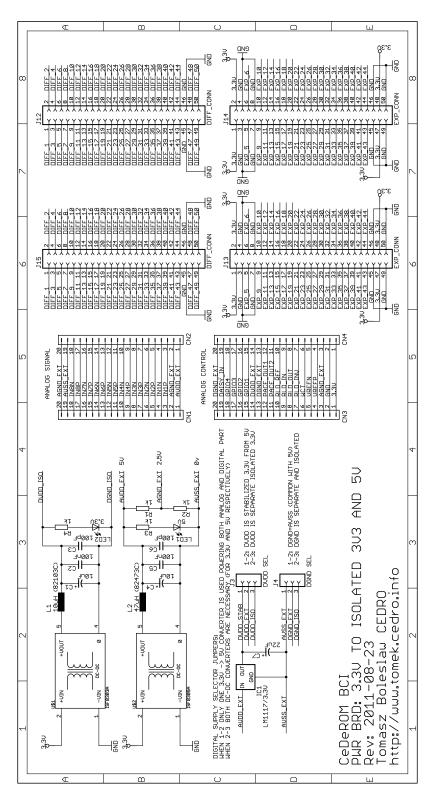

| 2.10 | CeDeROM BCI Power Board: 3.3V to isolated 3.3V and 5V Converter 94                                                                                 | 8 |

| 2.11 | CeDeROM BCI Power Board PCB design                                                                                                                 | 9 |

| 2.12 | CeDeROM BCI Power Board: 3.3V to isolated 3.3V and 5V Converter,                                                                                   |   |

|      | assembled. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $39$                                                                     | 9 |

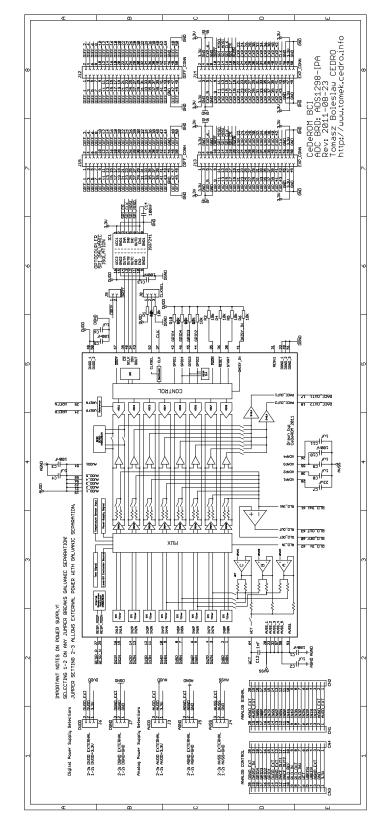

| 2.13 | CeDeROM BCI Analog–To–Digital Conversion Board: ADS1298-IPA (TQFP                                                                                  |   |

|      | footprint). $\ldots \ldots \ldots$ | 0 |

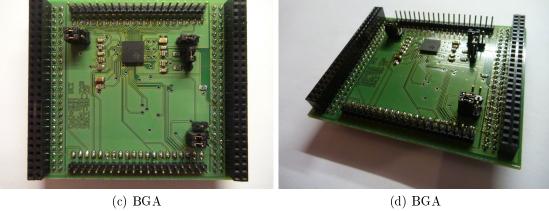

| 2.14 | CeDeROM BCI Analog–To–Digital Conversion Board: ADS1298-IPA (BGA                                                                                   |   |

|      | footprint)                                                                                                                                         |   |

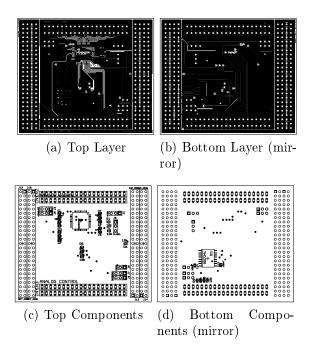

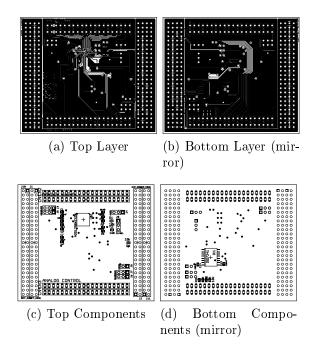

| 2.15 | CeDeROM BCI Analog–To–Digital Conversion Board based on TQFP ADS1209-                                                                              |   |

|      | IPA, PCB design                                                                                                                                    | 2 |

| 2.16 | $CeDeROM \ BCI \ Analog-To-Digital \ Conversion \ Board \ based \ on \ BGA \ ADS 1209-$                                                            |   |

|      | ZXG, PCB design                                                                                                                                    |   |

| 2.17 | CeDeROM BCI Analog–To–Digital Conversion Board based on BGA ADS1209–                                                                               |   |

|      | ZXG, PCB design                                                                                                                                    |   |

|      | CeDeROM BCI EEG Electrodes Board for ADS1298 Schematics 10                                                                                         |   |

|      | CeDeROM BCI ADS1298 EEG Electrodes Board PCB design 10                                                                                             |   |

|      | CeDeROM BCI ADS1298 EEG Electrodes Board, assembled 10                                                                                             | 6 |

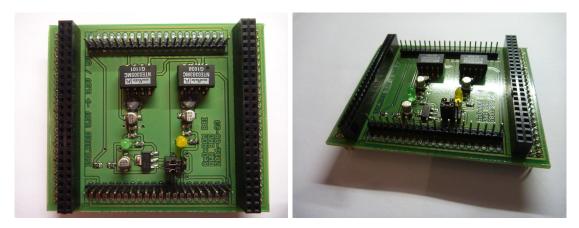

| 2.21 | CeDeROM BCI General Purpose Analog-To-Digital Conversion Board:                                                                                    | _ |

| 0.00 | ADS1278-IPA (TQFP footprint)                                                                                                                       | 1 |

| 2.22 | CeDeROM BCI General Purpose Analog-To-Digital Conversion Board                                                                                     | 0 |

| 0.00 | based on TQFP ADS1278–IPA, PCB design                                                                                                              | 8 |

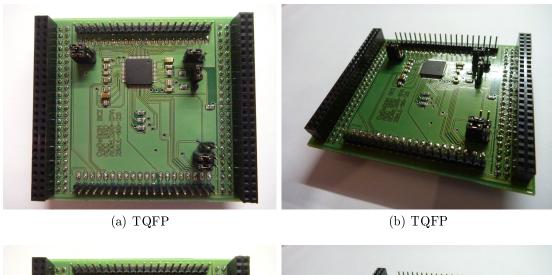

| 2.23 | CeDeROM BCI General Purpose Analog–To–Digital Conversion Board                                                                                     | 0 |

| 0.04 | based on TQFP ADS1278–IPA, assembled boards photos                                                                                                 |   |

|      | CeDeROM BCI Expansion Board: Atari Joystick Schematics                                                                                             |   |

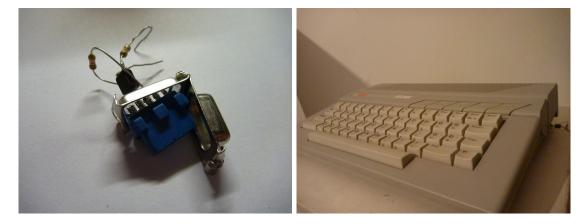

|      | CeDeROM BCI Expansion Board: Atari Joystick PCB design                                                                                             |   |

|      | First steps of joystick interface design and testing on my precious Atari 11                                                                       |   |

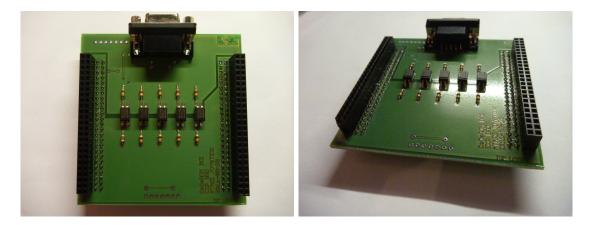

|      | CeDeROM BCI Joystick Expansion Board, assembled                                                                                                    |   |

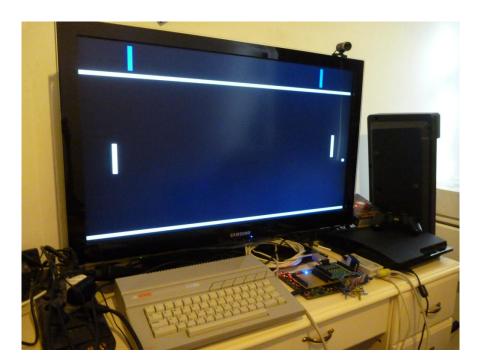

|      | CeDeROM BCI FPGA acting as standalone PONG videogame 11.<br>CeDeROM BCI FPGA acting as (Atari) videogame controller                                |   |

|      | CeDeROM BCI FPGA acting as (Atari) videogame controller                                                                                            |   |

|      | CeDeROM BCI ARM (left) replacement for OpenEEG (right)                                                                                             |   |

|      | Free applications to work with OpenEEG–like devices                                                                                                |   |

| 4.94 | GENT/ OF S HOULDE TEAUY OF USE WITH CEDENOINI DOL                                                                                                  | υ |

# Chapter 1

# Know-How

# 1.1 Reasons, Problems, Solutions.

Having planned tasks that will bring research, or any kind of computer-related project, into an end with no obstacles has become a wishful thinking. Unfortunately there are too much independent variables that makes planning a modern art of risk management rather than precise work navigation along timeline. Especially when advanced solution is created from scratch, there are even more complications and problems to solve, often possible solutions bring even more problems.

This process is hard to understand by the final user, as he/she wants to simply have cheap, working, stable and good looking, preferably one-click solution. Users nowadays already lost insight into system internals, some of them even don't want to know how things work as they tend to think that everything can be already bought (or ordered online). It has become a reality that for most people science or engineering is not much different from black magic. Marketing tricks makes things even worse because they model a happy unaware end-user that can posses years of work of thousands of intellectuals for a dollar, so users start to think they posses all those skills and knowledge as they own its results, never even wondering how it was possible to make it work. Therefore real value and importance of this knowledge is far more valueable and fundamental.. and it has never been only about new products.

The dilema of balancing between time and final cost is usually about what can be bought and integrated into final solution to shorten time-to-market but increase final price. This is also crucial factor for project planning, management and development. There is no need to manufacture single transistors or integrated cirtuit at some point when cheaper and faster application can be found with no significant impact on the income and result, but on the other hand there is no innovation in rebranding existing products. Real innovation begins where challenge is set to do something that never been done before in a way that was previously unknown or unsuccessful. Most manufacturers however exploit unaware users to produce simple low-quality products, enslave them with habits to manipulate future sale with fake innovation.

Independence is very important for me, even at cost of longer project timeline, not

only because of limited resources as those are always too small, mainly because I am not only a model consumer anymore, I want to consciously create my own solutions to share or sale with benefit. This chapter contains technical difficulties I have found during my research and description of invented solutions. Most of them were caused because I have decided to use only *Commercial Off The Shelf (COTS)* elements and Free Open Source Software and avoid repacking existing expensive solutions stating they are mine results.

Sharing experience with other individuals, using pieces of their work for my results, saving resources, gaining new skills, having independent solution with full insight unlimited with restrictive licenses – these are only few reasons why I have chosen this implementation path. Know–How presented in this chapter will also allow estimate work amount necessary to create such simple project from scratch. It may also help estimate real cost of a solution and realize complexity standing behind the scenes.

# **1.2** Biological Signal Amplifiers

According to [9] biological amplifiers are described by following parameters:

• Amplifier Gain is the output voltage level referenced to the voltage acquired by the amplifier circuit on its inputs. Usually the gain value is at least 1000 in linear scale, it can be also measured in decibels (dB):

$$Gain_{lin} = \frac{U_{out}}{U_{in}}$$

$$Gain_{dB} = 20 log_{10} Gain_{lin}$$

• Frequency Response is a characteristics in frequency domain describing useful bandwidth together with other frequencies and their relation in acquired signal. Useful bandwidth should contain all frequencies present in the electrophysiological signal generated by a tissue or organ of interest, while other frequencies should be limited accordingly to disallow impact of low frequency  $(f_l)$  drift and high frequency  $(f_h)$  interferences caused by surrounding technical environment on the target signal. Both low and high frequency cutoff is set at 0.707 value of midfrequency plateau, that is half of the useful signal power (because  $(0.707)^2 = 0.5$ ), this is why they are also called -3dB points and the difference between  $f_h$  and  $f_l$  is the 3dB bandwidth.

$$-3dB = 20log_{10}0.707$$

• Common Mode Rejection is very important parameter in differential  $(U_d)$  signal measurement where two electrodes are used for single source measurement to discard common signals  $(U_c)$ . This method is very useful in biological signals measurement where magnitudes of useful signal are thousands times smaller than external interferences caused by the power network or electronic equipment having similar potential across the human body acting as antenna.

$$CMMR_{lin} = \frac{U_c}{U_d}$$

CeDeROM Brain Computer Interface

$CMMR_{dB} = 20log_{10}CMMR_{lin}$

- Noise and Drift are the additional and unwanted signals in the measurement result produced by the amplifier circuit, electrode-skin contact, etc. Drift refers to signals below 0.1Hz and it is a peak-to-peak variation of the baseline, while noise above 0.1Hz measured in microvolts peak-to-peak ( $\mu V_{p-p}$ ) or microvolts root mean square ( $\mu V_{RMS}$ ).

- *Recovery Time* is the time necessary for amplifier circuit return from saturation to normal operation.Saturation can be caused by electrodes contact malfunction, stimulation currents, defibrillation pulses, or any other stimuli that pushes amplifier output voltage to reach the maximum/minimum offset voltage of constant value that prevents device from proper measurement.

- Input Impedance of the amplifier circuit should be high enough to prevent attenuation of useful signal produced by a tissue. Each electrode-tissue has its own characteristic impedance related to many factors such as the electrode-skin contact quality, electrolyte substrate and its temperature, are of the electrode, tissues between source tissue and the electrode, etc. The average impedance values are in range of  $200k\Omega$  for 1Hz and  $200\Omega$  for 1MHz.

- Electrode Polarization is the half-cell polarization caused by ion-electron exchange between metal electrode and electrolyte paste or simply skin perspiration that result in a DC component in a measured signal. Association for the Advancement of Medical Instrumentation (AAMI) specify that ECG equipment should tolerate  $\pm 300mV$  DC component resulting from the electrode-skin contact.

There are many more different configurations of biological signals amplifiers designs and theory with practical examples presented in [9] therefore it is highly advised to get familiar with this great book, as there is no sense to rewrite its contents in this small document.

# 1.3 System Configuration and Methodology

Each area of life seems to have a trend that leads the (research) directions in a defined period of time until something better is invented and become a new trend. This includes electronic design that nowadays tend to shift from analog design into digital domain with analog circuity reduced to absolute minimum. This allows better miniaturization, lower system cost, higher availability with smaller POF (Point Of Failure), better scalability and system reconfiguration in future without total redesign now replaced with firmware upgrade. Personally I don't think such blind trends-follower attitude is glorifying, but in this particular case it is very close to my intuition.

Biomedical equipment also use this "digitalization" trend to minimize analog components amount in the design and use better digital components that provide equivalent or better capabilities when implemented as software algorithms in programmable logic. BurrBrown company, now owned by Texas Instruments, leading world class manufacturer of components for biomedical instrumentation has released a series of documents and devices to pioneer these new fields of biomedical technologies. Analog filtering is replaced by DSP (Digital Signal Processing), analog components are replaced by high-end digital solutions, devices become more and more integrated.

I have joined this trend not only because I have better experience in digital electronics design, but also in my opinion they are more agile and give better flexibility in commercial application of different services and solutions. It is always possible to hire someone highly–skilled that will design the subsystem component, but the big–picture is more important for me – to create working solution. I have presented below some documents found in the knowledge base, they cover various aspects of modern design, they are available for free download on the BurrBrown/Texas Intruments website and I will place their contents in the Appendix. There are whole books being written on how to build analog amplifiers. I will use those information and results as modules for creating my solution instead. Documents presented below are also very important and valuable source of information for any designer of biocybernetic instrumentation:

- "Improving Common-Mode Rejection Using the Right-Leg Drive Amplifer" [10]

- "High Speed Data Conversion" [11]

- "Analog-to-Digital Converter Grounding Practices Affect System Performance" [12]

- "Interleaving Analog-to-Digital Converters" [13]

- "Thermal Noise Analysis in ECG Applications" [14]

- "Principles of Data Acquisition and Conversion", [15]

- "Analog Front-End Design for ECG Systems Using Delta-Sigma ADCs" [16]

- "A Glossary of Analog-to-Digital Specifications and Performance Characteristics" [17]

- "What Designers Should Know About Data Converter Drift" [18]

- "Power Management for Precision Analog" [19]

My solution will be based on high-resolution analog-to-digital conversion with minimal analog components amount. One usecase contain fully integrated device for biological signals acquisition (ADS1298 chip), another usecase contain general purpose highresolution analog-to-digital converter that can be attached to any compatible analog frontend. For more information please follow the "Solution Approach" (Chapter 2.1).

Figure 1.1: 10–20 EEG Electrode Placement Diagram [85].

## 1.4 EEG 10–20 system

The 10-20 system is a standard introduced to describe electrodes placement on top of the scalp (head skin) during the EEG measurement. This is important to reproduce and compare measurements over time on different subjects, because selected test points mark regions of underlying cerebral cortex that produces the internal signal received by the electrodes. The name 10-20 actually comes from the distance parts in left-right (10%) front-back (20%) length of the skull (Figure 1.1).

As described in [22] each site has a letter to identify the lobe and a number to identify the hemisphere location. The letters F, T, C, P and O stand for Frontal, Temporal, Central, Parietal, and Occipital, respectively. Note that there exists no central lobe, the "C" letter is only used for identification purposes only. A "z" (zero) refers to an electrode placed on the midline. Even numbers (2,4,6,8) refer to electrode positions on the right hemisphere, whereas odd numbers (1,3,5,7) refer to those on the left hemisphere. Two anatomical landmarks are used for the essential positioning of the EEG electrodes: first, the nasion which is the point between the forehead and the nose; second, the inion which

Figure 1.2: Commercial low-cost BCI devices for home use.

is the lowest point of the skull from the back of the head and is normally indicated by a prominent bump. When recording a more detailed EEG with more electrodes, extra electrodes are added utilizing the spaces in-between the existing 10-20 system. This new electrode-naming-system is more complicated giving rise to the Modified Combinatorial Nomenclature (MCN). This MCN system uses 1, 3, 5, 7, 9 for the left hemisphere which represents 10%, 20%, 30%, 40%, 50% of the inion-to-nasion distance respectively. The introduction of extra letters allows the naming of extra electrode sites. Note that these new letters do not necessarily refer to an area on the underlying cerebral cortex.

# 1.5 OpenEEG and other BCI Platforms

OpenEEG [84] is the most popular low-cost platform for amateur BCI/Neurofeedback research with fully open schematics (Figure 1.3) and internal support available to the community that gathered around this project for the past 8 years. There are some disadvantages of the platform. Hardware design is already outdated as it use 8-bit micro-controller with 8-bit ADC and RS232 for data transmission (modern computes does not have this port even available). Analog amplifier is not equipped with 50/60Hz notch filter so the power interferences are sometimes blocking the measurement, or the device needs voodoo style shielding. This is however the reference platform for many other designs, including one presented in this doument.

Some alternative to the OpenEEG system may be provided by the commercial BCI devices from NeuroSky [88] or Emotiv [89] companies. Because they are commercial and closed source they seem to be poor research equipment with their limited and non-customizable design. Commercial high-end equipment is provided by gTec.at [90] for well funded BCI research groups around the world to have standarized working environment.

There are several applications that can work with OpenEEG system, including Open-ViBE [86] for BCI interaction in Virtual–Reality environment, BCI2000 [85] well known BCI framework, BrainBay [87] and many more. One of the biggest disadvantages of these programs however is the fact that they work only on Windows, some of them are not

(a) Analog Part Schematics

(b) Digital Part Schematics

Figure 1.3: OpenEEG Schematics.

open-source so it is not possible to fix bugs in relatively old releases, some of them are restricted by licensing constraints. These programs however are the best (often also the only) choice home or academic user can get to experiment with BCI systems.

# **1.6** FreeBSD – Operating System of a choice

There are many computer operating systems on the market. Some of them free, some commercial, all protected with some kind of licensing agreement. Each one of them have some advantages and features making is usable more in some specific applications than the others. The system of a choice for my research is a well known Berkeley Software Distribution Unix Operating system named FreeBSD [34]. It is free, open source, compatible with most open source applications, and it has very simple license that allows closing final application. The FreeBSD can be considered a distribution of BSD system, just like OpenBSD, NetBSD and others. Commercial example of BSD application is very popular Apple Mac OS X for desktop machines and iPhoneOS for mobile machines, also lots of network and embedded equipment use this operating system for closed source applications.

Unlike Linux, FreeBSD is better organized and more self-compatible with other installations (one command or configuration file will work among all FreeBSD installations, what can't be said about Linux distributions, as each one of them is different, even among releases of one distribution, almost each new kernel release breaks existing drivers, etc). This is very important to have stable and independent working environment, especially in long term projects, where its configuration and internals does not make your work obsolete after few weeks or constantly require additional fees. Maintenance is very important part of the project life cycle. Microsoft exactly knows that and offers easy to configure Windows platform with multiple development tools. All those tools allow rapid development with no need to know details of implementation, but they are also commercial, relatively expensive and low quality, they require constant upgrades to non-backward compatible formats, so user ends up constantly spending money for something that is a black-box and cannot be expanded or customized. Other operating systems are usually dedicated for backend specific tasks, therefore require dedicated hardware platform what makes them unavailable and often useless for average computer user.

FreeBSD is free and less resource hungry, so it can run even on simple embedded systems, also does not double price of the final product. Its license does not put any constrains on application and the source code distribution. Although well organized structure and stable standard, the main disadvantage of the FreeBSD STABLE line is the lag behind modern multimedia features available only to the commercial systems. Also drivers for new gadgets and hardware are hard to find or simply waiting to be written. On the other hand this non-bleeding-edge development line is what makes it stable and straightforward solution. People that want to bring new features should consider developing CURRENT branch, where like in Linux, things change day by day and are not guaranteed to work or maintain backward compatibility. After new features are well tested and comply internal standards, they are (then and only then) integrated into STABLE line.

FreeBSD has proven to be most innovative and well organized solution for many years being ahead of competitors in some areas even driving development of new features for many other operating systems including Linux and Windows. Its very logical organization, maybe even raw in its simplicity, makes this system good candidate for stable working environment that can be controlled with a simple set of text configuration files and standard Unix/POSIX environment and utilities. This system does not hide anything from user in a form of invisible automation unless explicitly asked to do so. It is also free of external dependencies, even on Free Software, so neither deveopers nor users are forced to buy upgrade or pay additional money for trivial additional features. There are also nice features available uncommon to any other operating systems, for instance binary emulation of other operating systems including BSD and Linux allowing for transparent binary runtime execution. Therefore all futher chapters will assume FreeBSD operating system was used unless stated otherwise.

# 1.7 GNU ARM Toolchain

GNU ARM Toolchain [25] is a free of charge and Open Source set of tools to develop software that will run on ARM machine. The toolchain consists of the GNU binutils, compiler set (GCC) and debugger. Newlib is used for the C library. The toolchain includes the C and C++ compilers. It comes fully documented – with online books for developers, and system man pages for each of the tools provided. Users familiar with Unix or Unix-like operating systems will have no problem with GNU ARM tools, as they are the same as the ones used to build programs on x86, x86\_64, mips, and many other platforms:

- arm-elf-gcc is a GNU compiler of a C programming language. Object files produced by this program contains binary code executed by ARM microprocessor.

- arm-elf-as is an GNU assemmbly language compiler. It uses AT&T UNIX syntax (different than Intel) to parse input and produces binary code of almost any microprocessor architecture.

- arm-elf-ld is a GNU Linker program that produces final executable or even whole system image from a separate object files. This program requires special configuration file (\*.ld) with memory map (rom+flash+ram) of a target ARM system to produce \*.hex or \*.bin image matching configuration of a specific silicon chip.

- arm-elf-gdb is a GNU Debugger. This tool allows watching target program execution instruction-after-instruction and helps finding bugs in code. This program also allows remote debug of a physical target plaform connected via JTAG interface to the host running debug daemon software (ie. OpenOCD). Remote debug can be performed with use of TCP/IP network, so the user is not limited to the direct neighbourhood of the device.

• gnu make – this program is not a part of the GNU ARM Toolchain, but is common GNU tool available on most Unix or Unix-like environments. This program controls the generation of executables and other non-source files of a program from the program's source files. It is indispensable program that automates build process of a final executable code or system image. It reads instructions, on how to react on command line parameters, from a special configuration file called Makefile.

There are also few others commercial Software Development Kits (SDK) for ARM family, but I will not discuss them here, as they are expensive and windows platform dependent in most cases. GNU SDK is a standard set of tools to develop software in a free and platform independent way. Also system requirements for this software is far beyond expectations of the modern commercial toolkits. Once the developer learn how to work with GNU tools, it will be no difference whether he/she writes software for a computer or embedded system, and what hardware platrofm is inside – it will be only a matter of few configuration files and program switches. What is more, the whole development process takes place in a shell (command line) environment, so it can be performed remotely via simple terminal program, from any place linked to an internet. For those who prefer graphical and windowed development environment, there is a special release called YAGARTO [27] to work with Eclipse Integrated Desktop Environment (IDE) [26].

All this is for free, so the real price goes for knowledge and skills of a user. This fact is really worth appreciation to the developers of the GNU Project [24] and The Free Software Foundation [23].

# 1.8 Free Real Time Operating System

## 1.8.1 Introduction

FreeRTOS is a free real-time operating system ported to many different hardware platforms, targeted to use with embedded systems. FreeRTOS gives developer ability to create multitasking environment with multiple tasks or co-routines that can be sorted by priority, sharing resources by queues, synchronising by semaphore and mutex technique. Within its small footprint (approximately 25kB) there are both aviable simple dynamic memory allocation (malloc) and Interrupt Servicing Routine (ISR) mechanisms. Please refer for project homepage http://www.freertos.org for detailed information.

# 1.8.2 API Fundamentals

The kernel is the core component within an operating system. Operating systems such as Linux employ kernels that allow users access to the computer seemingly simultaneously. Multiple users can execute multiple programs apparently concurrently. Each executing program is a task under control of the operating system. If an operating system can execute multiple tasks in this manner it is said to be multitasking. The use of a multitasking operating system can simplify the design of what would otherwise be a complex software application:

- The multitasking and inter-task communications features of the operating system allow the complex application to be partitioned into a set of smaller and more manageable tasks.

- The partitioning can result in easier software testing, work breakdown within teams, and code reuse.

- Complex timing and sequencing details can be removed from the application code and become the responsibility of the operating system.

#### 1.8.2.1 Task

FreeRTOS versions prior to V4.0.0 allow a real time application to be structured as a set of autonomous 'tasks' only. This is the traditional model used by an RTOS scheduler.

A real time application that uses an RTOS can be structured as a set of independent tasks. Each task executes within its own context with no coincidental dependency on other tasks within the system or the scheduler itself. Only one task within the application can be executing at any point in time and the real time scheduler is responsible for deciding which task this should be. The scheduler may therefore repeatedly start and stop each task (swap each task in and out) as the application executes. As a task has no knowledge of the scheduler activity it is the responsibility of the real time scheduler to ensure that the processor context (register values, stack contents, etc) when a task is swapped in is exactly that as when the same task was swapped out. To achieve this each task is provided with its own stack. When the task is swapped out the execution context is saved to the stack of that task so it can also be exactly restored when the same task is later swapped back in.

Task Summary:

- Simple.

- No restrictions on use.

- Supports full preemption.

- Fully prioritised.

- Each task maintains its own stack resulting in higher RAM usage.

- Re-entrancy must be carefully considered if using preemption.

#### 1.8.2.2 Co-routine

FreeRTOS version V4.0.0 onwards allows a real time application to optionally include co-routines as well as, or instead of, tasks. Co-routines are conceptually similar to tasks but have the following fundamental differences (elaborated further on the co-routine documentation page): Stack usage. All the co-routines within an application share a single stack. This greatly reduces the amount of RAM required compared to a similar application written using tasks. Co-routines use prioritised cooperative scheduling with respect to other co-routines, but can be included in an application that uses preemptive tasks. The co-routine implementation is provided through a set of macros. The reduction in RAM usage comes at the cost of some stringent restrictions in how co-routines can be structured.

Co-Routine Summary:

- Sharing a stack between co-routines results in much lower RAM usage.

- Cooperative operation makes re-entrancy less of an issue.

- Very portable across architectures.

- Fully prioritised relative to other co-routines, but can always be preempted by tasks if the two are mixed.

- Lack of stack requires special consideration.

- Restrictions on where API calls can be made.

- Co-operative operation only amongst co-routines themselves.

#### 1.8.2.3 API Selection

Only those API functions specifically designated for use from within an ISR (Interrupt Service Routine) should be used from within an ISR, as ISR stands for Interrupt Service Routine and is designed only to serve IRQ. Tasks and co-routines use different API functions to access queues. A queue cannot be used to communicate between a task and a co-routine or visa versa. Intertask communication can be achieved using the full featured API functions, the alternative API functions, and the light weight API functions (those with "FromISR" in their name). Use of the light weight functions outside of an ISR requires special consideration, as described under the heading "Performance tips and tricks - using the light weight API". For more detailed information please browse the Documentation at http://www.freertos.org.

# 1.9 Universal Serial Bus

## 1.9.1 Introduction

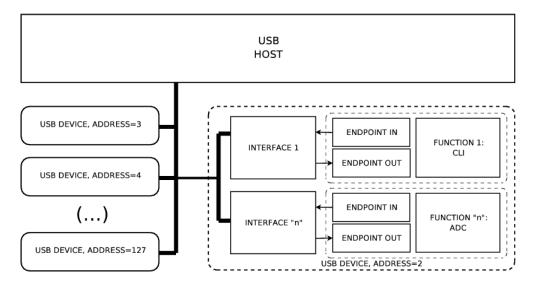

USB stands for Universal Serial Bus, a serial interface to exchange data between computer and peripherials. It uses Plug'n'Play Host-Device architecture, where Host is responsible for all data manipulation on the bus, device identification and driver load/unload, while Device can receive or send data when asked by the Host. Device can be dynamically connected and disconected without need to turn off or restart computer. Devices are identified by PID and VID number pair (Product and Vendor ID) along with Identifier String. There are many different Transfer Modes to fit needs of a specific project. USB Device can have more than only one interface using common physical connection.

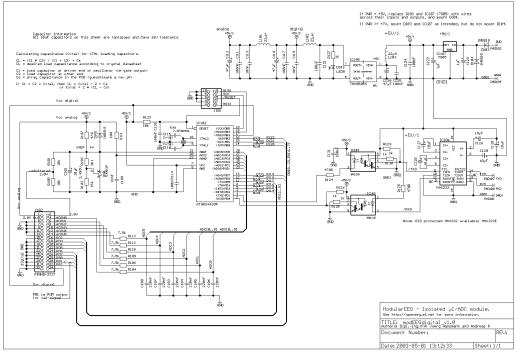

Figure 1.4: Command Line Interface (CLI) implemented on LPC2148 ARM-based microcontroller with built–in USB Device Controller using OpenSource programs.

This chapter is just an overview of the USB Bus features, to get more detailed information, but not yet reading full specification that is really really big, I highly recommend reading "USB in a NutShell" [33] freely available e-book.

#### 1.9.2 Standards

Current version of USB standard is 3.0, but it is not yet widely deployed in computer hardware, so we will still use version 2.0, the successor of the USB 1.0 and 1.1 specification [32]. It uses EHCI (Encanced Host Controller Interface) specification. There can be up to 127 devices on the bus, connected one Port via HUB (star architecture). HUB can perform current mesurement and dynamic load/unload devices that interrupts the BUS. Devices connected this way shares bandwith of the Port. If more bandwith or devices are to be connected, Host with more Ports should be used.

There are two types of connectors used in USB: A for upstream/Host, B for downstream/Device. Data Cable consists of four signals: 5V, D+, D-, GND. Data is transferred differentially on D+ and D- lines, using NRZI (Non Return to Zero Inverted) and bit stuffing. D+ and D- lines are also used as control lines (nondifferential) at reset and enumeration phase, just after connecting Device to the Host.

USB 2.0 Device can support one or two of three speed modes:

$\bullet$  Low Speed 1.5MB it/s, accuracy 1.5 % or 15000ppm

- $\bullet$  Full Speed 12MB it/s, accuracy 0.25 % or 2500ppm

- High Speed 480MBit/s, accuracy 500ppm

#### 1.9.3 Physical Signalling

USB trasnmitter defines differential '1' by pulling D+ over 2.8V with 15k resistor tied to ground, and pulling D- under 0.3V with 1.5k resistor tied to 3.6V. Logical '0' is inversion of logical '1'. The receiver identifies '1' when D+ is 200mV higher than D- line, and '0' when D- line is 200mV above D+. The polarity of the signals might be inverted depending on the current Speed Mode - so called 'J' state for Low Speed is represented by differential '0', while it is differential '1' in High Speed mode.

It is important to select proper series resistors for impedance matching for D+ and D- lines. Low and Full Speed Modes has characteristic impedance of 90ohms with 15% accuracy. High Speed also uses 17.78mA constant current for signalling to reduce noise.

Device indicates its speed mode by pulling high (3.3V via 1.5k resistor) appropriate data line: D+ to mark Full/High Speed or D- to mark Low Speed. High and Full Speed modes are selected the same way electrically, but the reset and enumeration phase selects proper protocol.

Device can support only Low and Full Speed modes and no High Speed mode, to make product cheaper. When device supports High Speed then it also support Full Speed but no Low Speed.

#### 1.9.4 Power Management

USB Devices can be powered from within the Host requiring no externel power supply. Device should know how much current it will consume and give this value to the Host during Enumeration Phase in 2mA quants. USB also specifies Unit Load as 100mA. This divides Devices into three categories:

- 1. Low-Power: can draw only one unit load, and must work within 4.4V to 5.25V range measured on upstream plug

- 2. High-Power: can draw maximum 5 unit load (500mA) after enumeration phase but 1 unit load before enumeration, and Vbus ranging from 4.75V to 5.25V.

- 3. Self-Powered: may draw 1 unit load from the bus to allow detection without external power turned on; must have external power supply to operate.

No device can drive Vbus - after Host turns off Vbus, Device must deactivate pullups on the D+ and D- lines that are used for speed identification.

Device must support Suspend Mode. Global Suspend will work for each Device on the bus, while Selective Suspend can work only for selected ones. One unit load stands for 500uA suspend current. Attention should be taken that pullup resistors sinks 200uA all the time. Device should put itself in Suspend Mode when there is no activity in the bus for 3 miliseconds and has 7 ms to acomplish this task. After 10ms of silence on the bus, the Device should not sink more than designated Suspend Current, but the Host can send special kepalive packets to the Device to avoid suspend on the bus with no data:

- High Speed: micro-frames sent every 125 us  $+-62.5 \mathrm{ns}$

- Full Speed: frames sent every 1ms +-500ns

- Low Speed: EOP (End of Packet) sent every 1ms in case of data absence on the bus

Device should resume operation after receiving any non idle signaling, and should report to the Host if it has been resumed from any other reason.

#### 1.9.5 USB Procotol

USB is more complicated than standard UART where pure bytes of data are being sent and received transparently one after another. USB consists of advanced logical structure that determines many different functions that can be implemented in a single device. That is why there must be an USB Stack implemented in a Software, supported by a Hardware Block that performs low level transactions and timings conforming to the USB Bus standard [32].

Figure 1.5: Host centric USB bus organisation

Transfer with a Device is always initiated by a Host and the "IN" transfer direction is always directed towards Host. "OUT" transfer means "from the Host to the Device", while "IN" transfer means "from the Device to the Host". Each transaction consists of three parts of data:

• Token Packet – says what kind of transfer is being performed (IN, OUT, SETUP)

- Data Packet is optional packet containing the payload

- Status Packet provides acknowgledge or error correction data (ACK, NAK, STALL)

There can be as many as 128 devices connected to a single bus in a slave manner – that is Device cannot transmit anything itself. If a specific Function of the Device wants to transmit or receive any data it must use "End Point" (EP) as a kind of transmit buffer and wait for the Stack/Hardware and Host to perform Bus Transaction. But to use and End Point, the Device Stack has to be initialised and setup with proper parameters (Transfer Mode, Interface number, buffer length, etc) described by a set of an USB Descriptors.

#### 1.9.6 USB Transfer Modes

#### 1.9.6.1 Interrupt Transfer

Works similar to an interrupt on the computer – when the USB Device needs to report some activity it waits until being polled by a Host, and then transfers some small amount of data. It guarantees small latency, it is bidirectional (Stream Pipe) and supports error detection and retransfer in next period. The maximum data payload is

- 8 bytes for Low Speed

- 64 bytes for Full Speed

- 1024 bytes for High Speed

#### 1.9.6.2 Isochronous Transfer

This mode can be used to transfer data periodicaly or continously in time sensitive applications like audio or video streaming. No delivery or retry is guaranted, and error correction is provided only by CRC, although USB bandwidth is guaranted with bounded latency. This transfer mode is unidirectional using Stream Pipe. Maximum data packet size is 1024 bytes for High Speed and 1023 for Full Speed mode. Low Speed mode does not support this transfer mode. Also there is no handshake (no Handshake Packet), so errors and STALL/HALT cannot be reported.

#### 1.9.6.3 Bulk Transfer

This mode can be used to transfer bursts of data that do not need low latency. Because bulk transfer mode uses unallocated bandwidth of the USB Bus, it should not be used in time sensitive applications, as it will have to wait for others isonchronous and interrupt transfers with preallocated bandwidth. This mode is Unidirectional using Stream Pipes, and supports error detection based on CRC and retransmission if necessary.

## 1.9.7 Bandwidth Mangement

It is possible to allocate bandwith for an USB Device at enumeration stage of the Isonchronous and Interrupt Endpoints. Host is then responsible for managing the requested bandwidth. Maximum 90% for Full Speed Bus and 80% for High Speed Bus can be selected. The rest is reserved for Control and Bulk Transfers.

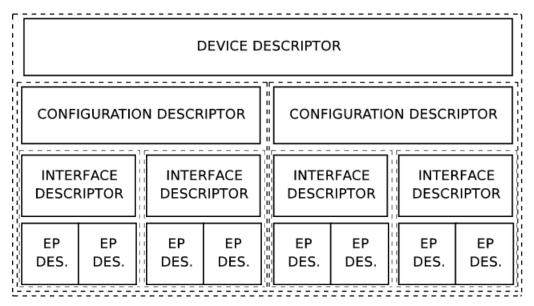

## 1.9.8 USB Descriptors

Descriptors are defined by the software as a part of the logical structure of the USB Device. Besides dedicated silicon hardware that performs bit-level communication with the Host, Device Descriptors are the most important part of the Device itself, because they define all of its internal organisation – name, identification and manufacturer, bus version support, available configurations, internal interfaces, transfer modes, buffer lengths, and many more.

Figure 1.6: USB Device Descriptors organisation diagram

Descriptors perform following functions:

- Device Descriptor it contains information such as USB Bus compliance, Product and Vendor ID (PID/VID pair to recognise device and load apropriate drivers), and number of possible configurations.

- Configuration Descriptor tells how much power does the current configuration requires and how many interfaces it has. One device can have many different configurations. At the enumeration stage host can iterate all of these possible configurations (maximum amount is defined by the Device Descriptor) to choose one that is possible to achieve or selected by the end user. Only one configuration can be choosen at a time.

- Interface Descriptor groups endpoints (EP) based on a specific function of the USB Device. Interface can be described as one of many logical devices inside a one hardware, because one USB Device can perform many different functions at the same time.

- EndPoint Descriptor specifies type of transfer, direction, packet size, polling interval. EndPoint is a source or sink of data. Endpoint number zero is a control endpoint and has no descriptor.

- String Descriptor is optional and contains human readable information encoded in Unicode format. Strings can contain multilanguage contents.

# 1.10 Device Drivers in Matlab

#### 1.10.1 Introduction

Designing advanced data acquisition systems requires whole set of methods to verify a prototype and the data that it produces. This can be achieved by use of Matlab [29], or free Matlab-like software (ie. Octave [30], SciLab [31], or similar). With its wide spread of signal spectrum analysis, filter design and data modelling techniques, this is perfect environment for research related activities. Data can be transferred from device hardware into matlab environment by use of commercial Data Acquisition Toolbox and standard data bus, or design specific dedicated data bus and self written device driver. This section describes how to create a dedicated device driver in Matlab, from sctratch.

## 1.10.2 How Matlab handles execution

Matlab can generate binary executables basing on its standard m-files (Compiler Toolbox), but can also use external binaries or dynamic libraries to perform required operations. We can use these features to write our own driver. Please read matlab manual page named "External Interfaces" for detailed information. Input-Output routines and cooperation with external applications are available thanks to:

- dynamic libraries (so/dll) support

- external C of Fortran procedure calls within MEX file

- creating MEX files in C or Fortran language

- result data import/export with MAT files

- including Matlab code fragments in C or Java applications

Device Driver is usually a set of functions performing device configuration and data transfer. In Matlab environment this can be implemented as set of MEX files or standard dynamic library. MEX files are Matlab specific, can be written in C or Fortran language,

and they are easier in later use. Dynamic libraries can be written in any programming language, used by any other application, and they are just a bit harder in later use with Matlab. Dynamic libraries are preffered method in this document. Please take a look at *"MATLAB Interface to Generic DLLs"* Matlab Manual section for detailed information.

## 1.10.3 Dynamic Libraries Matlab Intefrace

Dynamic library is a kind of container that holds many functions in a predefined manner. There are few specific initialisation functions and the others can operate on data passed in as pointers. Because all library contents can be dynamically loaded at runtime, there can be many functions with the same name grouped in a different libraries performing different functions. This is how the plugins work - required content is loaded into runtime memory only when its needed.

Functions included in a dynamic library can be loaded into Matlab runtime memory and become accesible directly from the interpreter commadline. In most cases data cast is automatic and Matlab types are preffered. Dynamic Libraries can also be written in languages other than C, but the library interface must conform to the C dynamic library standard.

## 1.10.4 Using Dynamic Libraries

#### 1.10.4.1 Opening the library

To acces functions included in a dynamic library, use loadlibrary routine:

```

loadlibrary('library_name', 'header_filename')

```

where:

- library\_name is a dynamic library filename (\*.so or \*.dll)

- header\_filename is a header filename (\*.h) with all of the function names and data types used by the dynamic library

#### 1.10.4.2 Closing the library

To close a dynamic library that is already open, use unloadlibrary routine:

unloadlibrary library\_name

#### 1.10.4.3 Browsing the library

To display a dynamic library contents, use libfunctions or libfunctionsview routines:

```

libfunctions('library_name')

libfunctionsview('library_name')

```

where:

- libfunctions returns string array with function names from selected library

- libfunctionsview function names from selected library are displayed as table in a separate window

Both functions can use **-full** switch to display additional functions information (ie. parameter list, data types, etc.)

#### 1.10.4.4 Calling the library functions

To call a function that is included in a opened dynamic library, use callib routine:

```

calllib('library_name', 'function_name', arg1, ..., argN)

```

where:

- library\_name is an opened dynamic library

- function\_name is a function that we want to call

- arg1,..,argN is a function argument list

#### 1.10.5 Example

As an example we want to use three functions included in one dynamic library. Two of them will return string (character array) and the last one return sum of passed arguments.

The header file test.h:

```

1 char* test();

2 char* test2();

3 int test_add(int a, int b);

```

The source file test.c:

```

#include "test.h"

1

\mathbf{2}

char* test(){

return "test function 1 result\n";

3

4

}

char* test2(){

5

return "test function 2 result\n";

6

}

7

int test add(int a. int b){

8

9

return a+b;

}

10

```

Building the library with GNU C Compiler:

```

1 gcc -shared -o test.so test.c

```

Now the Matlab part:

Page 30 of 125

```

>> cd path_to_our_library

1

2

>> loadlibrary test.so test.h

>> calllib('test', 'test')

3

4

ans =

test function 1 result

5

>> calllib('test', 'test2')

6

7

ans =

test function 2 result

8

9

>> calllib('test', 'test_add')

??? Error using ==> calllib

10

No method with matching signature.

11

>> calllib('test', 'test_add', 1, 2)

12

13

ans =

14

3

15

>> unloadlibrary test

```

## 1.11 Serial Wire Debug

Serial Wire Debug [43] is a new low-level embedded system access introduced by ARM Corporation [42] in their new CPU design ARMv7 named Cortex. It is compliant to ARM Debug Interface version 5 [44] that specifies all requirements and capabilities of this transport. We will call it transport, because its purpose is to transport commands between debug software on the host computer and debug port on the target system, just as JTAG does, but in a different fashion. JTAG use state machine design, while SWD use packed-based half duplex serial link with lower pin count than JTAG.

ARM is a company that designs CPU and license that design as IP (Intellectual Property) to a silicon manufacturer company that puts some additional peripherials around and sell this as a physical chip for a device of some kind. ARM Cortex devices appeared on the market around year 2008 bringing new quality to mobile world, somehow synchronized with Google Android OS entrance to the market. In year 2011 we have Cortex-A8 family dominating the market with commercially available product and this year Cortex-A9 comes to light with multicore CPU support. There are plans for Cortex-A15 in 2012 having even more computational power, more cores, multimedia peripherials, etc. Cortex family is on its way to the top, being manufactured by silicon gigants such as Samsung [49], Qualcomm [50], Texas Instruments [51], ST Microelectonics [52] and others. It will soon fill the growing market of tablet, laptop, set-top-box and other embedded devices.

Having already insight and tools to work with this new Serial Wire Debug transport gives an apportunity to work with upcoming devices in near future and gain skills on already existing ones. Creating development tools before developers can have it is also great benefit. The LibSWD I have created is the **first in the world open implementation** of the Serial Wire Debug Open Framework already integrated with UrJTAG [37] and OpenOCD [36] low-level embedded systems access software utilities.

There are still a lot of things to do in order to access other, deeper, parts of the CPU and trace/debug facilities, but the first step has been done – recognising the transport mechanism logical and physical construction of Serial Wire Debug, creating LibSWD [38] and integrating it with existing software utilities, attracting the community around the subject for further development stimulation.

## 1.11.1 Serial Wire Debug Technical Reference

#### 1.11.1.1 Introduction

This section contains essential information to understand how SWD transport works, how it is organized, what bus commands are available, what is the Debug Access Port (DAP), Debug Port (DP), Access Port (AP), and how all this works. Information contained in this section are based on copyrighted by ARM Corporation [42] Arm Debug Interface version 5 manual [44] and more specific to our example device ARM Cortex-M1 Reference Manual [45]. For detailed information refer to the ARM Info Center [46].

#### 1.11.1.2 Signalling

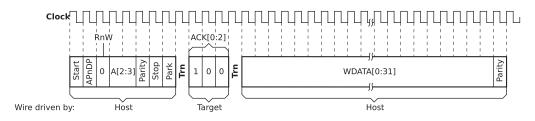

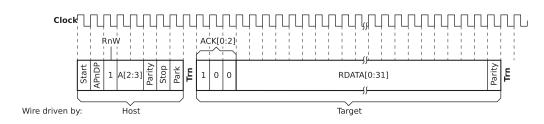

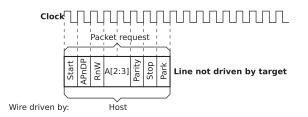

SW-DP (Serial Wire Debug Port) operates with a synchronous serial interface. This uses a single bidirectional data signal SWDIOTMS and a clock signal SWCLK (and the GROUND signal ofcourse). Each sequence of operations on the wire consists of two or three phases:

- Packet request The external host debugger issues a request to the debug port. The debug port is the target of the request.

- Acknowledge response The target sends an acknowledge response to the host.

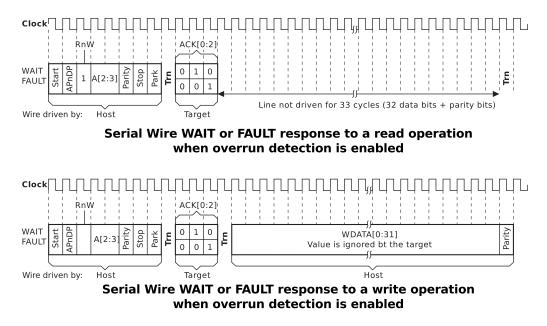

- Data transfer phase This phase is only present when either:

- Data Read or Data Write request is followed by a valid (OK) acknowledge response.

- ORUNDETECT flag is set to 1 in the CTRL/STAT Register (if CTRL/STAT=1 then data transfer is required on all responses).

The data transfer is one of:

- target to host, following a read request (RDATA)

- host to target, following a write request (WDATA).

The SW-DP uses a serial wire for both host and target sourced signals. The host emulator drives the protocol timing. Only the host emulator generates packet headers. Both the target and host are capable of driving the bus HIGH and LOW, or tristating it. Time required to switch from transmission into receiving mode is called **Turnaround** time.

The SW-DP clock, SWCLKTCK, can be asynchronous to the device/system CLK. SWCLKTCK can be stopped when the debug port is idle, but host must continue to clock the interface for a number of cycles after the data phase of any data transfer – this ensures that the transfer can be clocked through the SW-DP. 100k high-pullup resistor is recommended at target on SWTMSIO line, therefore this line should be driven high before entering low power mode.

#### 1.11.1.3 Interface Reset and Synchronization

Interface reset or resynchronization occurs at 50 clocks with data line set high and then IDCODE read ended with OK response. Device will signal request for reset by not driving the data line at response stage, after two bad data sequences in a row target locks out and requests reset sequence described before. Additionally host should give target some time for command processing to return a payload, host can request IDCODE read and when it fails it should reset Target.

Note: After reset and jtag-to-swd sequence SWDIOTMS line must be driven low with at least one clock pulse on SWCLK line, otherwise target will not respond to any request! JTAG-TO-SWD sequence presented by ARM is incomplete and will not work without IDLE cycle. It is good to implement IDLE command that consists of SWDIOTMS line set low with 8 clock pulses on SWCLK line (kind of request with 0x00 payload) that will allow SW-DP to successfully complete commands execution when appended at the end of long queue or reset sequences.

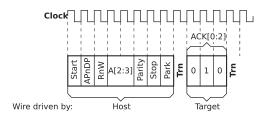

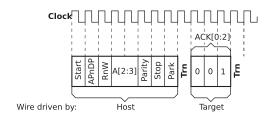

#### 1.11.1.4 SWD Packet Construction

- Start single start bit, with value 1.

- APnDP single bit, indicating whether the DP or the AP Access Register is to be accessed. This bit is 0 for a DPACC access, or 1 for an APACC access.

- RnW single bit, indicating whether the access is a read or a write. This bit is 0 for an write access, or 1 for a read access.

- A[2:3] two bits, giving the A[3:2] address field for the DP or AP Register Address (shifted out LSB first):

- APACC access, the register being addressed depends on the A[3:2] value and the value held in the SELECT register.

- DPACC access, the A[3:2] value determines the address of the register in the SW-DP register map.

- Parity single parity bit for the preceding packet.

- Stop single stop bit. In the synchronous SWD protocol this is always 0.

- Park single bit. The host must drive the line high before tristating the line. The target reads this bit as 1.

- TRN (Turnaround) this is a period when the line is not driven and the state of the line is Undefined. The length of the turnaround period is controlled by the TURNROUND field in the Wire Control Register. The default setting is a turnaround period of one clock cycle. By default turnaround time is one cycle.

- ACK 3-bit target-to-host response. Transmitted LSB first on the wire.

- WDATA[0:31] 32 bits of write data, from host to target.

- RDATA[0:31] 32 bits of read data, from target to host.

In the SWD protocol, a simple parity check is applied to all packet request and data transfer phases. Parity bit appears on the wire immediately after the A[2:3] bits (ACK[0:2] bits are never included in the parity calculation). Even parity is used:

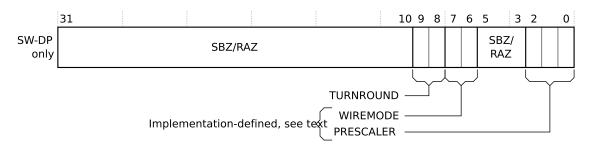

- Packet requests parity check is made over the APnDP, RnW and A[2:3] bits (when the number of bits set to 1 is odd then the parity bit is set to 1, when the number of bits set to 1 is even then the parity bit is set to 0).